# **NINA-B50** series

## Stand-alone Bluetooth 5.3 low energy modules

**Data sheet**

### Abstract

Targeted towards system integrators and design engineers, this technical data sheet includes the functional description, pin definition, specifications, country approval status, handling instructions, and ordering information for NINA-B50 series Bluetooth<sup>®</sup> 5.3 Low Energy modules. NINA-B50 provides an open CPU architecture with a powerful MCU for developing customer applications.

## **Document information**

| Title                         | NINA-B50 series                              |            |

|-------------------------------|----------------------------------------------|------------|

| Subtitle                      | Stand-alone Bluetooth 5.3 low energy modules |            |

| Document type                 | Data sheet                                   |            |

| Document number               | UBX-22021114                                 |            |

| Revision and date             | R04                                          | 8-Mar-2024 |

| <b>Disclosure restriction</b> | C1-Public                                    |            |

| Product status                   | Corresponding content status                                                          |                                                                                        |  |  |

|----------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

| Functional sample                | Draft For functional testing. Revised and supplementary data will be published later. |                                                                                        |  |  |

| In development /<br>Prototype    | Objective specification                                                               | Target values. Revised and supplementary data will be published later.                 |  |  |

| Engineering sample               | Advance information                                                                   | Data based on early testing. Revised and supplementary data will be published later.   |  |  |

| Initial production               | Early production information                                                          | Data from product verification. Revised and supplementary data may be published later. |  |  |

| Mass production /<br>End of life | Production information                                                                | Document contains the final product specification.                                     |  |  |

### This document applies to the following products:

| Product name | Ordering code | Type number      | Hardware version | IN/PCN<br>reference | Product<br>status     |

|--------------|---------------|------------------|------------------|---------------------|-----------------------|

| NINA-B501    | NINA-B501-00A | NINA-B501-00A-00 | 01               | N/A                 | Functional sample     |

| NINA-B506    | NINA-B506-00A | NINA-B506-00A-00 | 01               | N/A                 | Functional sample     |

| NINA-B501    | NINA-B501-00B | NINA-B501-00B-00 | 06               | N/A                 | Initial<br>Production |

| NINA-B506    | NINA-B506-00B | NINA-B506-00B-00 | 07               | N/A                 | Initial<br>Production |

u-blox or third parties may hold intellectual property rights in the products, names, logos, and designs included in this document. Copying, reproduction, or modification of this document or any part thereof is only permitted with the express written permission of u-blox. Disclosure to third parties is permitted for clearly public documents only. The information contained herein is provided "as is" and u-blox assumes no liability for its use. No warranty, either express or implied, is given, including but not limited to, with respect to the accuracy, correctness, reliability, and fitness for a particular purpose of the information. This document may be revised by u-blox at any time without notice. For the most recent documents, visit www.u-blox.com. Copyright © u-blox AG.

# Contents

| Documer  | nt information                                                 | 2  |

|----------|----------------------------------------------------------------|----|

| Contents | ð                                                              | 3  |

| 1 Funct  | tional description                                             | 6  |

| 1.1 Ove  | erview                                                         | 6  |

| 1.2 App  | olications                                                     | 6  |

| 1.2.1    | Professional application examples                              | 6  |

| 1.2.2    | Automotive application examples                                | 6  |

| 1.3 Blo  | ck diagram                                                     | 7  |

| 1.4 Pro  | duct variants                                                  | 7  |

| 1.4.1    | NINA-B501                                                      | 7  |

| 1.4.2    | NINA-B506                                                      | 8  |

| 1.4.3    | Professional grade variants                                    | 8  |

| 1.4.4    | Automotive grade variants                                      | 8  |

| 1.5 Pro  | duct description                                               | 8  |

| 1.6 Sof  | tware                                                          | 9  |

| 1.7 Blu  | etooth device address                                          | 9  |

| 2 Inter  | faces                                                          |    |

| 2.1 Pov  | ver management                                                 | 10 |

| 2.1.1    | Power switch                                                   | 10 |

| 2.1.2    | DC-DC, digital I/O, analog, and system input supply (VCC_IO)   | 10 |

| 2.1.3    | Power supply configuration                                     | 11 |

| 2.2 2.4  | GHz radio                                                      | 11 |

| 2.3 RF   | antenna interfaces                                             | 11 |

| 2.3.1    | Internal antenna                                               | 11 |

| 2.3.2    | External antenna                                               | 11 |

| 2.4 Sys  | stem functions                                                 | 12 |

| 2.4.1    | Power modes                                                    | 12 |

| 2.4.2    | Module reset                                                   | 13 |

| 2.4.3    | CPU and memory                                                 | 14 |

| 2.4.4    | ROM bootloader                                                 | 14 |

| 2.4.5    | Enhanced Direct Memory Access (eDMA)                           | 15 |

| 2.4.6    | Real Time Clock (RTC)                                          | 15 |

| 2.5 Ser  | ial interfaces                                                 | 16 |

| 2.5.1    | Low Power Universal Asynchronous Receiver/Transmitter (LPUART) | 16 |

| 2.5.2    | Low-power serial peripheral interface (LPSPI)                  | 17 |

| 2.5.3    | Low Power Inter-Integrated Circuit (LPI2C)                     | 18 |

| 2.5.4    | Improved Inter-Integrated Circuit (I3C)                        | 18 |

| 2.5.5    | Flexible input/output (FlexIO)                                 | 19 |

| 2.5.6    | FlexCAN                                                        | 20 |

| 2.5.7    | LIN                                                            | 21 |

| 2.6  | Other digital interfaces                                 | 21                                                                                                                                                                                                                                                                                                                                                                |

|------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.6  | 6.1 Timer/ PWM (TPM)                                     | 21                                                                                                                                                                                                                                                                                                                                                                |

| 2.6  | 6.2 Quadrature Decoder (QDEC)                            | 22                                                                                                                                                                                                                                                                                                                                                                |

| 2.7  | Analog interface                                         | 22                                                                                                                                                                                                                                                                                                                                                                |

| 2.7  | 7.1 Analog to Digital Converter (ADC)                    | 22                                                                                                                                                                                                                                                                                                                                                                |

| 2.7  | 7.2 Low Power Comparator (LPCMP)                         | 23                                                                                                                                                                                                                                                                                                                                                                |

| 2.7  | 7.3 Voltage Reference (VREF)                             | 23                                                                                                                                                                                                                                                                                                                                                                |

| 2.7  | 7.4 Analog pin options                                   | 24                                                                                                                                                                                                                                                                                                                                                                |

| 2.8  | GPIO                                                     | 24                                                                                                                                                                                                                                                                                                                                                                |

| 2.8  | 8.1 Drive strength                                       | 24                                                                                                                                                                                                                                                                                                                                                                |

| 2.9  | Debug interfaces                                         | 24                                                                                                                                                                                                                                                                                                                                                                |

| 2.9  | 9.1 SWD                                                  | 24                                                                                                                                                                                                                                                                                                                                                                |

| 2.9  | 9.2 DAP                                                  | 25                                                                                                                                                                                                                                                                                                                                                                |

| 2.9  | 9.3 SWO                                                  | 25                                                                                                                                                                                                                                                                                                                                                                |

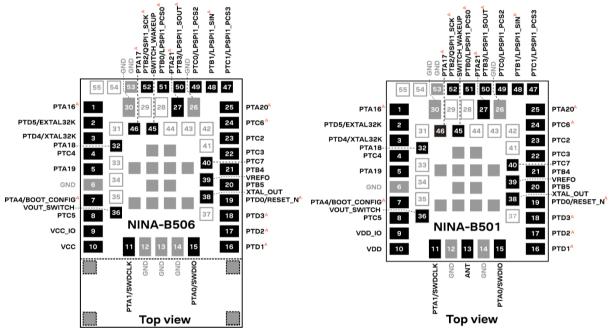

| Pi   | in definition                                            | 26                                                                                                                                                                                                                                                                                                                                                                |

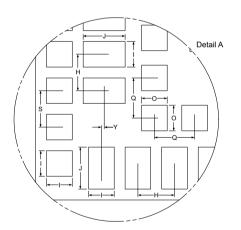

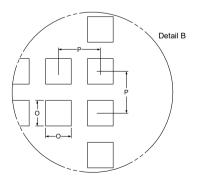

| 3.1  | NINA-B50 series pin assignment                           | 26                                                                                                                                                                                                                                                                                                                                                                |

| Ele  | lectrical specifications                                 | 32                                                                                                                                                                                                                                                                                                                                                                |

| 4.1  | Absolute maximum ratings                                 | 32                                                                                                                                                                                                                                                                                                                                                                |

| 4.1  | 1.1 Maximum ESD ratings                                  | 32                                                                                                                                                                                                                                                                                                                                                                |

| 4.2  | Operating conditions                                     | 33                                                                                                                                                                                                                                                                                                                                                                |

| 4.2  | 2.1 Operating temperature range                          | 33                                                                                                                                                                                                                                                                                                                                                                |

| 4.2  | 2.2 Supply/Power pins                                    | 33                                                                                                                                                                                                                                                                                                                                                                |

| 4.3  | Current consumption                                      | 33                                                                                                                                                                                                                                                                                                                                                                |

| 4.4  | RF performance                                           | 34                                                                                                                                                                                                                                                                                                                                                                |

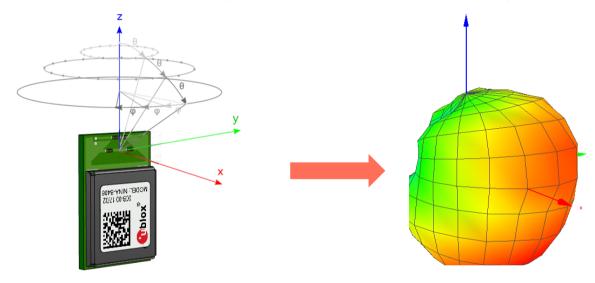

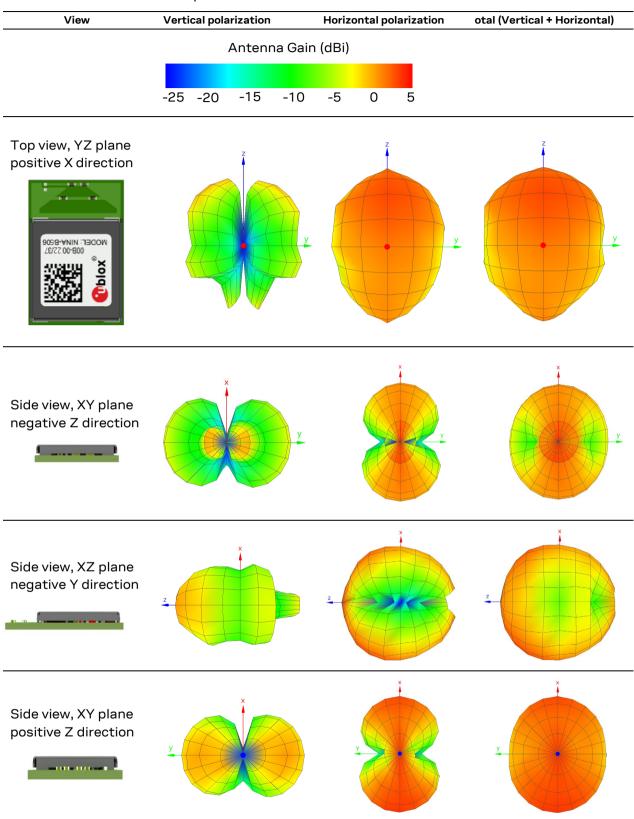

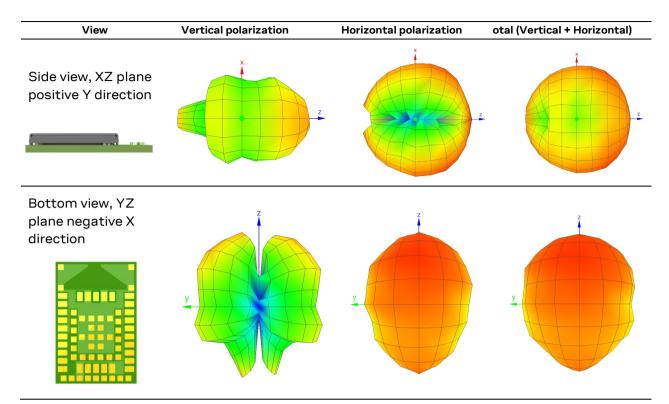

| 4.5  | Antenna radiation patterns                               | 35                                                                                                                                                                                                                                                                                                                                                                |

| 4.6  | 32 kHz FRO                                               | 37                                                                                                                                                                                                                                                                                                                                                                |

| 4.7  | External 32 kHz crystal oscillator                       | 37                                                                                                                                                                                                                                                                                                                                                                |

| 4.8  | RESET_N pin                                              | 38                                                                                                                                                                                                                                                                                                                                                                |

| 4.9  | Digital pins                                             | 39                                                                                                                                                                                                                                                                                                                                                                |

| 4.10 | ) Analog comparator                                      | 40                                                                                                                                                                                                                                                                                                                                                                |

| M    | lechanical specifications                                | 41                                                                                                                                                                                                                                                                                                                                                                |

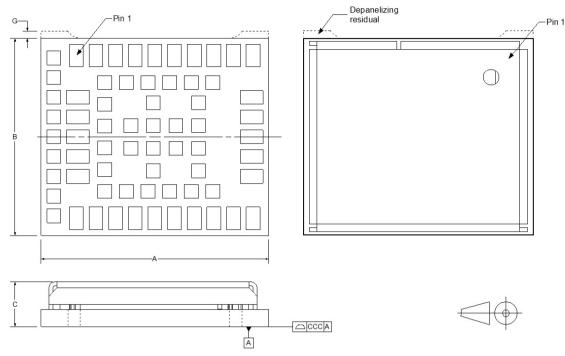

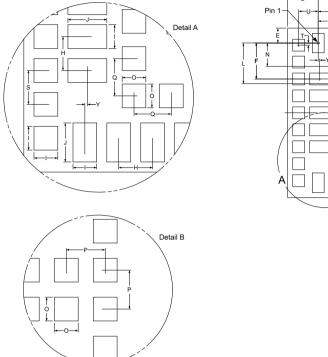

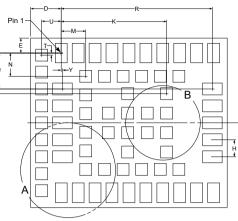

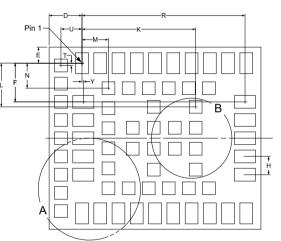

| 5.1  | NINA-B501 mechanical specification                       | 41                                                                                                                                                                                                                                                                                                                                                                |

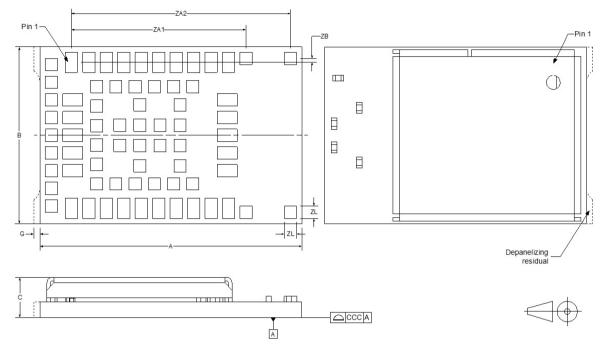

| 5.2  | NINA-B506 mechanical specification                       | 43                                                                                                                                                                                                                                                                                                                                                                |

| Qı   | ualifications and approvals                              | 45                                                                                                                                                                                                                                                                                                                                                                |

| 5.1  | Compliance with the RoHS directive                       | 45                                                                                                                                                                                                                                                                                                                                                                |

| 5.2  | Country approvals                                        | 45                                                                                                                                                                                                                                                                                                                                                                |

| 5.3  | Bluetooth qualification                                  | 45                                                                                                                                                                                                                                                                                                                                                                |

| Pr   | roduct handling                                          | 46                                                                                                                                                                                                                                                                                                                                                                |

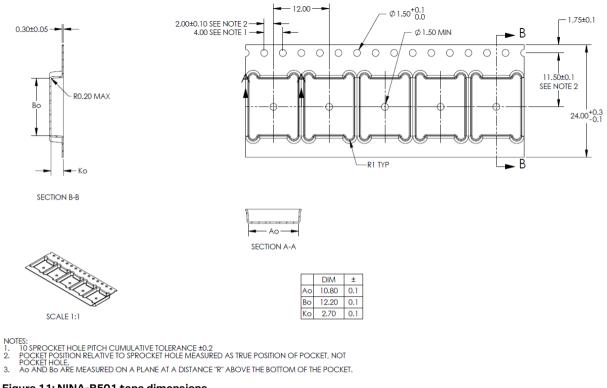

| 7.1  | Packaging                                                | 46                                                                                                                                                                                                                                                                                                                                                                |

| 7.   | 1.1 Reels                                                | 46                                                                                                                                                                                                                                                                                                                                                                |

| 7.   | 1.2 Tapes                                                | 46                                                                                                                                                                                                                                                                                                                                                                |

| 7.2  | Moisture sensitivity levels                              | 48                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.<br>2.7<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2<br>2 | 2.6.1  Timer/PWM (TPM)    2.6.2  Quadrature Decoder (QDEC)    2.7  Analog interface    2.7.1  Analog to Digital Converter (ADC)    2.7.2  Low Power Comparator (LPCMP)    2.7.3  Voltage Reference (VREF)    2.7.4  Analog pin options    2.8  GPIO    2.8.1  Drive strength    2.9  Debug interfaces    2.9.1  SWD    2.9.2  DAP    2.9.3  SWO    Pin definition |

| 7.3 Reflow soldering4                 | 8  |

|---------------------------------------|----|

| 7.4 ESD precautions4                  | 8  |

| 8 Labeling and ordering information 4 | 9  |

| 8.1 Product labeling4                 | .9 |

| 8.1.1 Product identifiers5            | 0  |

| 8.1.2 Identification codes5           | 0  |

| 8.2 Ordering information5             | ;1 |

| Appendix                              | 2  |

| A Glossary                            | 2  |

| Related documentation                 | 3  |

| Revision history                      | 3  |

| Contact                               |    |

# **1** Functional description

## 1.1 Overview

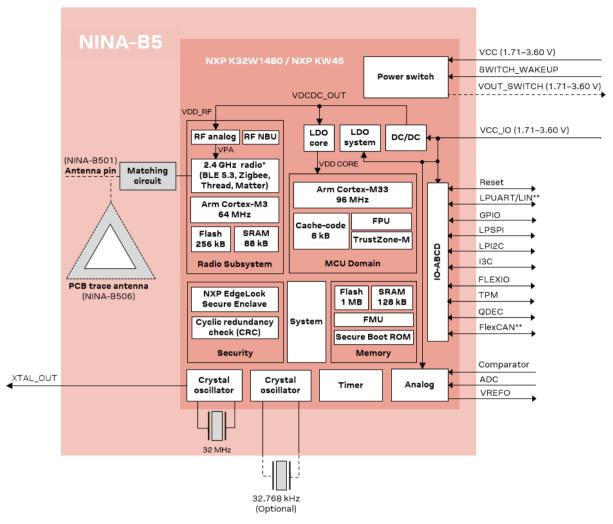

Built on the NXP K32W1480 chip [3] for professional applications and NXP KW45 chip [5] for automotive applications, NINA-B50 series modules feature Bluetooth 5.3 LE connectivity and a robust multicore MCU with an Arm<sup>®</sup> Cortex<sup>®</sup>-M33 supporting a Floating Point Unit (FPU) as the application core.

NINA-B50 module series offer cutting-edge power performance and incorporates state-ofthe-art security features through the Arm TrustZone-M<sup>®</sup> secure storage and EdgeLock<sup>®</sup> Secure Enclave – including hardware cryptographic accelerators, random number generators, secure key generation, storage and management, secure boot and secure debug.

For professional applications, NINA-B50 supports IEEE 802.15.4 including Thread<sup>®</sup>, Matter™, and Zigbee™. For automotive applications, NINA-B50 supports FlexCAN and LIN bus.

As the module design of NINA-B50 is common with other modules following the NINA form factor, NINA-B50 offers flexibility for similar product variants when designing the host platform.

## 1.2 Applications

### 1.2.1 Professional application examples

- Industrial automation

- Smart buildings and cities

- Low power sensors

- Wireless-connected and configurable equipment

- Point-of-sales

- Healthcare

### 1.2.2 Automotive application examples

- Keyless entry

- Sensor hub

- LED-light control

- Battery management system

- Tachograph

## 1.3 Block diagram

\* IEEE 802.15.4 (Thread<sup>®</sup>, Matter<sup>™</sup>, and Zigbee<sup>™</sup>) is only supported by NINA-B50 professional grade modules. \*\* FlexCAN and LIN bus are only supported by NINA-B50 automotive grade modules.

Figure 1: Block diagram of NINA-B50 series

## 1.4 Product variants

The NINA-B50 series modules consist of modules with two different antenna options, each in two different product grades. NINA-B501 supports an antenna pin for use with external antennas, while NINA-B506 includes an integrated PCB antenna. Both product variants are available in either professional or automotive grade.

### 1.4.1 NINA-B501

NINA-B501 has no internal antenna. The RF signal for routing to an external antenna or antenna connector signal is exposed through a dedicated module pin (ANT). The module size of the NINA-B501 is smaller than that of the NINA-B506 ( $10.0 \times 11.6 \times 2.38 \text{ mm}$ ).

### 1.4.2 NINA-B506

NINA-B506 is equipped with an internal PCB trace antenna, using antenna technology licensed from Abracon. The RF signal is connected to the internal PCB trace antenna directly and is not connected to any pin on the module. The module size is  $10.0 \times 15.0 \times 2.38$  mm.

### 1.4.3 Professional grade variants

Built on the AEC-Q100 grade 2 NXP K32W148 chip, professional-grade module variants support not only Bluetooth Low Energy but also IEEE 802.15.4 for Thread, Zigbee, and Matter. The operating temperature for these variants is -40 to +85 °C. The modules are qualified and manufactured in accordance with u-blox professional grade policy [7], which is based on a subset of AEC-Q104.

### 1.4.4 Automotive grade variants

Built on the AEC-Q100 grade 2 NXP KW45 chip, automotive-grade module variants support Bluetooth Low Energy radio and additional CAN FD and LIN bus interfaces. The operating temperature for these variants is -40 to +105 °C. The modules are qualified and manufactured in accordance with u-blox automotive grade policy, which is based on AEC-Q104 and ISO/TS 16949.

## 1.5 Product description

| Item                                                                               | NINA-B501                                                                    | NINA-B506                                                                    |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Radio chipset, professional grade module<br>Radio chipset, automotive grade module | NXP K32W1480 [3]<br>NXP KW45B41Z83AFTB [5]                                   | NXP K32W1480 [3]<br>NXP KW45B41Z83AFTB [5]                                   |

| Supported 2.4 GHz radio protocols                                                  | Bluetooth 5.3 Low Energy<br>IEEE 802.15.4 -2015<br>(Thread, Matter, Zigbee)* | Bluetooth 5.3 Low Energy<br>IEEE 802.15.4 -2015<br>(Thread, Matter, Zigbee)* |

|                                                                                    | Bluetooth Low Energy specification                                           | on                                                                           |

| Operating channels and frequencies                                                 | 40 channels<br>Channel numbers 0–39<br>2402–2480 MHz                         | 40 channels<br>Channel numbers 0-39<br>2402–2480 MHz                         |

| Bluetooth LE data rates                                                            | 1 Mbps<br>2 Mbps<br>500 kbps (Coded PHY, S=2)<br>125 kbps (Coded PHY, S=8)   | 1 Mbps<br>2 Mbps<br>500 kbps (Coded PHY, S=2)<br>125 kbps (Coded PHY, S=8)   |

| Typical conducted output power**                                                   | +7 dBm / +10 dBm                                                             | +7 dBm / +10 dBm                                                             |

| Radiated output power (EIRP)**                                                     | +10 dBm / +13 dBm<br>with external 3 dBi antenna gain                        | +10 dBm / +13 dBm                                                            |

| Conducted RX sensitivity, 1 Mbps                                                   | -97.0 dBm                                                                    | -97.0 dBm                                                                    |

| Conducted RX sensitivity, 2 Mbps                                                   | -94.0 dBm                                                                    | -94.0 dBm                                                                    |

| Conducted RX sensitivity, long range 500 kbps<br>(Coded PHY, S=2)                  | -101 dBm                                                                     | -101 dBm                                                                     |

| Conducted RX sensitivity, long range 125 kbps<br>(Coded PHY, S=8)                  | -105 dBm                                                                     | -105 dBm                                                                     |

|                                                                                    | IEEE 802.15.4 specification*                                                 |                                                                              |

| Operating channels and frequencies                                                 | 16 channels<br>Channel numbers 11-26<br>2405–2480 MHz                        | 16 channels<br>Channel numbers 11-26<br>2405–2480 MHz                        |

| IEEE 802.15.4 data rate                                                            | 250 kbps                                                                     | 250 kbps                                                                     |

|                                                                                    |                                                                              |                                                                              |

| Item                               | NINA-B501                                          | NINA-B506                |

|------------------------------------|----------------------------------------------------|--------------------------|

| Typical conducted output power**   | +7 dBm / +10 dBm                                   | +7 dBm / +10 dBm         |

| Radiated output power (EIRP)**     | +10 dBm / +13 dBm<br>with external 3 dBi antenna g | +10 dBm / +13 dBm<br>ain |

| Conducted RX sensitivity, 250 kbps | -103 dBm                                           | -103 dBm                 |

|                                    | Module dimensions                                  |                          |

| Module size                        | 10.0 x 11.6 x 2.38 mm                              | 10.0 x 15.0 x 2.38 mm    |

|                                    |                                                    |                          |

Table 1: NINA-B50 characteristics summary

\* IEEE 802.15.4 (Thread<sup>®</sup>, Matter<sup>™</sup>, and Zigbee<sup>™</sup>) is only supported by professional grade NINA-B50 modules.

\*\* Depends on regulatory requirements and supply voltage level. For more details, see Table 11: RF performance.

## 1.6 Software

The open CPU architecture of the NINA-B50 series modules allows integrators to create their own applications by utilizing the comprehensive MCUXpresso SDK software from NXP. For more details, see the NINA-B50 system integration manual [2].

## 1.7 Bluetooth device address

Each NINA-B50 module is pre-programmed with a unique 48-bit Bluetooth device address. If the memory of a NINA-B50 module is erased or otherwise lost, the address can be recovered from the data matrix barcode printed on the module label, as described in Product labeling.

# 2 Interfaces

For optimal design flexibility, NINA-B50 supports a wide range of interfaces, including a 2.4 GHz radio and antenna interface, digital interface, analog interface, and debug interface. See also the NXP K32W1480 data sheet [3], NXP K32W1480 reference manual [4], NXP KW45 data sheet [5] and NXP KW45 reference manual [6].

## 2.1 Power management

### 2.1.1 Power switch

NINA-B50 modules include an on-module power switch that can be used to switch off all or part of MCU power supply. When activated, the power switch reduces the module power consumption to a level that is less than that achievable in the Deep Power Down mode. You can also use the switch to supply power to an external device through **VOUT\_SWITCH**.

The **VCC** input supply must be permanently applied to support both the standby RAM LDO and the RAM power switch. The power switch output signal, **VOUT\_SWITCH**, can be enabled or disabled.

The power switch can be turned on in several ways:

- Power-On-Reset (POR). This condition is triggered when the module is initially powered on or when the power level falls below the POR threshold. POR resets all power domains, including the supply input to the switch, VCC of power switch input supply **VCC**.

- Drive **SWITCH\_WAKEUP** low externally. The pin is internally pulled up to the switch input through a resistor and can be pulled down to wake up the smart power switch. To generate a valid internal wake-up signal successfully, a maximum pulldown voltage of 0.7 V on **SWITCH\_WAKEUP** is required. The duration time should be greater than 1 µs.

- Through the System Power Controller (SPC). The SPC contains internal wake-up logic that controls the operation of the power system. The switch activates when **VSYS** is powered on.

## 2.1.2 DC-DC, digital I/O, analog, and system input supply (VCC\_IO)

NINA-B50 modules require an additional voltage supply input **VCC\_IO**. This voltage supply, **VCC\_IO**, supply power for the following on-module function parts:

- DC-DC buck converter: Regulates the system core and radio power to provide the best power efficiency.

- LDO-System: A low-dropout regulator that generates the system voltage for the module.

- Analog domain, including an Analog-to-digital converter (ADC), comparators (CMP) and Voltage Reference (Vref) parts.

- Digital I/O interfaces

VCC\_IO must be supplied through either VCC or VOUT\_SWITCH. See also Power supply configuration.

### 2.1.3 Power supply configuration

NINA-B50 modules support two power supply configurations:

- Power efficient configuration

- Supply external power to VCC

- VCC\_IO supplied from VCC

- VDD\_LDO\_CORE and VDD\_RF supplied from the DCDC output

- VPA supplied from VDD\_RF

- Power switch configuration

- Supply external power to VCC

- Supply the power switch output VOUT\_SWITCH to VCC\_IO

- VDD\_LDO\_CORE and VDD\_RF are supplied from DCDC output

- VPA is supplied from VDD\_RF

- A voltage level less than 3 V on VCC and VCC\_IO has negative impact on the Tx output power.

- The on-module power switch can be disabled when it is not used. This means that the **VOUT\_SWITCH** pin can be floating.

- See also the System integration manual [2] for power management and power supply configuration.

## 2.2 2.4 GHz radio

NINA-B50 includes a 2.4 GHz radio transceiver that is integrated in K32W1480 chip or KW45 chip. The chip also incorporates an integrated balun that requires filter/matching circuitry, which is integrated inside the NINA-B50 modules. NINA-B50 modules also have an integrated 32 MHz crystal as source of radio clock of the modules. See also Block diagram.

For information about 32 MHz crystal trim value configuration, antenna reference designs, integration instructions and approved external antennas, see also the system integration manual [2].

## 2.3 RF antenna interfaces

NINA-B501 and NINA-B506 modules support different 2.4 GHz antenna solutions.

### 2.3.1 Internal antenna

NINA-B506 modules are equipped with an internal PCB antenna. This low-profile antenna solution is useful in space constrained designs and in designs that don't require an external antenna. The antenna pin (**ANT**) is internally disconnected on these modules. This solution uses antenna technology licensed from Abracon. See also antenna solutions in the System integration manual [2].

### 2.3.2 External antenna

NINA-B501 modules are equipped with an antenna pin (**ANT**) for connecting either an antenna connector or an external antenna. **ANT** is matched to 50  $\Omega$  and connected to the single-ended Tx/Rx antenna pin on the integrated 2.4 GHz radio transceiver in the K32W1480 or KW45 chip. The pin can be connected to an antenna connector or external antenna using a controlled impedance trace. See also antenna solutions in the System integration manual [2].

## 2.4 System functions

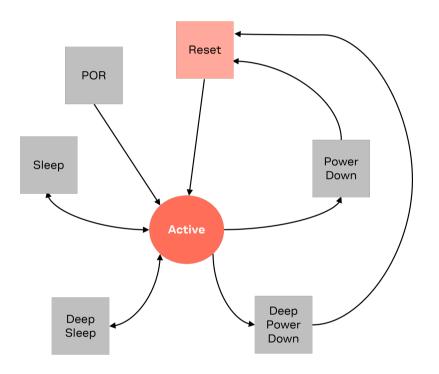

### 2.4.1 Power modes

NINA-B50 modules are power efficient devices that can operate in different power modes that control both power consumption levels and wake-up times. Specific parts of the module can be powered off when they are not needed. Complex wake-up events can also be generated from different external and internal inputs.

NINA-B50 supports several power modes:

- Active

- Sleep

- Deep Sleep

- Power Down

- Deep Power Down

Figure 2: NINA-B50 modules power modes

### 2.4.1.1 Active

When powered on or reset, NINA-B50 enters Active mode and is initialized according to the configuration defined in the application software flashed in the modules.

In Active mode, CPU execution is possible. To achieve the performance requirements of a given system application while minimizing power consumption. Active mode provides different power-saving options.

Any reset brings the module back to the Active mode.

### 2.4.1.2 Power Down

NINA-B50 modules do not have a dedicated pin for powering off. The Power Down mode puts the module in a power-off state. The module wakes up from Power Down mode through the reset routine.

### 2.4.1.3 Deep Power Down mode

In Deep Power Down mode, NINA-B50 modules operate at the lowest possible power level. In this mode, the entire **VDD\_CORE** domain (including all subdomains) is power gated and the on-module regulator for **VDD\_CORE** is powered off. The **VDD\_SYS** on-module regulator is powered, and the **VDD\_SYS** power domain is enabled.

To avoid extra leakage, the external power supply to any disabled on-module regulators should be turned off. Memory data held in static RAM (SRAM) cannot be retained in Deep Power Down mode.

The module wakes from Deep Power Down mode through the reset routine. External reset or the **VDD\_SYS** domain peripherals can wake the module.

### 2.4.1.4 Sleep

Sleep mode minimizes power consumption while maintaining the performance requirements of the system application.

In Sleep mode, CPU execution is halted. The core clock is gated off. The system clock as well as the bus clocks, if enabled, continue to operate.

Wake from Sleep mode is triggered by an interrupt or a wakeup event. Sleep mode also supports a partial wake-up where a bus controller other than the CPU, e.g., DMA is recovered by a wakeup event. The module automatically re-enters sleep mode after the bus controller finishes its task.

### 2.4.1.5 Deep Sleep

Deep Sleep mode sets NINA-B50 into a static state. It is the lowest power mode that retains all register data. The software can individually configure SRAM for deep sleep or shut down.

The module wakes from Deep Sleep mode through the interrupt routine or a wake-up event. Peripherals connected to the **VDD\_CORE\_WAKE** subdomain can wake the module. External signals can also wake the module through GPIO or **VDD\_SYS** domain peripherals.

### 2.4.2 Module reset

NINA-B50 can be reset in one of the following ways:

- Pin reset: A low level on the **RESET\_N** input pin.

- Power-on reset (POR): When supply voltage is below the POR threshold, the POR circuit triggers the power-on reset condition.

- Low Voltage Detect (HVD) reset: The HVD circuit is disabled by default. When the LVD is enabled and the supply voltage is above the HVD threshold, the circuit triggers an HVD reset.

- High Voltage Detect (LVD) reset: The LVD circuit is enabled by default. When the LVD is enabled and supply voltage is below the LVD falling threshold, the circuit triggers an LVD reset.

- Wakeup (WAKEUP) reset: When module wakes from Power Down or Deep Power Down modes, the power management logic triggers a wakeup reset in power domains that were previously powered off.

- Debug Access Port (DAP) reset: Any debug access port that can initiate a reset request from a connected debugger can trigger the DAP reset.

- Reset Timeout (RSTACK): The reset state machine includes a timeout counter that is triggered when the stack is inactive for more than 8192 cycles of the RTC 32.768 kHz clock. This condition triggers the RSTACK reset.

- Low Power Timeout (LPACK) reset: The low power entry state machine includes a timeout counter that is triggered if a module does not acknowledge entry into a low power mode after 8192 cycles of the RTC 32.768 kHz clock. This condition triggers the LPACK reset.

- System Clock Generation (SCG) reset: The system clock generator includes loss-of-clock and/or loss-of-lock monitors that can be configured to generate a reset. Either condition triggers the SCG reset.

- Software (SW) reset: When the software configures a system reset request in the MCU core.

- Watchdog 0 (WDOG0) reset: A watchdog timer monitors the software and expects periodic refreshing of the watchdog counter. A WDOG0 reset condition is triggered if the counter is not refreshed periodically.

- Watchdog 1 (WDOG1) reset: A watchdog timer monitors the software and expects periodic refreshing of the watchdog counter. A WDOG1 reset condition is triggered if the counter is not refreshed periodically.

- Lockup (LOCKUP) reset: Triggered when the Cortex-M33 core enters the lockup state as a result of certain illegal operations.

- JTAG (JTAG) reset: Occurs when a JTAG instruction places the module in reset.

- Security Violation (SECVIO) reset: Triggered when the module detects a security violation.

### 2.4.3 CPU and memory

NINA-B50 modules integrate an NXP K32W1480 or KW45 chip that includes an Arm Cortex-M33 MCU with FPU. The chip supports clock speeds of up to 96 MHz with 1 MB flash, 128 kB SRAM, 8 kB code cache for data storage and code, and 96 kB Secure Boot ROM that stores the boot code and time-critical software library routines.

NINA-B50 series modules include a multicore microcontroller unit (MCU) handling security, radio, and application tasks, where each core manages its own dedicated memory resources. Users can develop applications using the application core, which integrates an Arm Cortex-M33 MCU with an FPU, 1 MB flash memory, and 128 kB SRAM. NINA-B50 also provides an external memory connection to the Low-power serial peripheral interface (LPSPI).

### 2.4.4 ROM bootloader

The ROM bootloader is the boot code that resides in the internal read-only memory (ROM) of the module. The bootloader is executed when the host processor is released from reset. The code supports automated booting from the internal flash and downloads an image over the serial interface, LPUART, LPI2C, or LPSPI.

### 2.4.5 Enhanced Direct Memory Access (eDMA)

The enhanced Direct Memory Access (eDMA) can perform complex data transfers with minimal intervention from a host processor. The eDMA is a highly programmable data-transfer engine that is optimized to minimize any required intervention from the host processor. It is intended for use in applications where the data transfer is of a static size and not defined within the data itself.

### 2.4.6 Real Time Clock (RTC)

The Real Time Clock (RTC) is a key system feature of the module.

By default, the time counter in the RTC is driven from a 32.768 kHz clock, which can also supply other peripherals. The clock can be sourced from an external 32 kHz Crystal Oscillator (OSC) or an embedded 32 kHz Free Running Oscillator (FRO) on the module.

The RTC block includes an internal clock validation mechanism that ensures the clock from OSC is stable. It also incorporates a switch that allows the module to switch the clock source from the 32 kHz FRO to the OSC when it is stable. The module can switch back to the 32 kHz FRO clock if the software disables the 32 kHz OSC.

The 32 kHz FRO is enabled after Power-On-Reset (POR) and serves as the clock source to the device. The 32 kHz FRO can be disabled by the software when necessary.

The external 32 kHz OSC is disabled after POR but can be enabled by software when needed.

The RTC is an "always-powered" block that remains functional in all low power modes. It can generate an interrupt to exit any low-power mode.

The RTC operates in one of the two available modes of operation:

- Power-on mode. The RTC remains powered During module power-up. In this mode, all RTC registers are accessible by software and all functions are operational. If enabled, the 32.768 kHz clock can be supplied to the rest of the module.

- Power-down mode. During module power-down, the RTC remains powered and is electrically isolated from the rest of the chip. If enabled, the RTC continues to increment the time counter and retains the state of the RTC registers. The RTC registers are not accessible. The time counter can generate multiple interrupts and events for the CPU, radio, as well as the internal and external hardware blocks. By default, the frequency of the interrupt is 1 Hz, but it can also be configured to trigger every 2, 4, 8, 16, 32, 64, or 128 Hz.

| Signal        | I/O | Pinout | Description                                                                                                              |

|---------------|-----|--------|--------------------------------------------------------------------------------------------------------------------------|

| PTD5/EXTAL32K | I   | 2      | 32.768 kHz oscillator input, connection to an optional<br>external 32.768kHz crystal<br>Can be configured as a GPIO pin  |

| PTD4/XTAL32K  | 0   | 3      | 32.768 kHz oscillator output, connection to an optional<br>external 32.768kHz crystal<br>Can be configured as a GPIO pin |

| RTC_CLKOUT    | 0   | NA     | Prescaler square-wave output or RTC 32.768 kHz clock<br>Can be configured to get the signal via TAMPER1                  |

| RTC_WAKEUP_b  | 0   | NA     | Active low wakeup for external device<br>Can be configured to get the signal via TAMPER0                                 |

| RTC_TAMPER0   | I   | 17     | Tamper pin input                                                                                                         |

The RTC signals and pinout for NINA-B50 is shown in Table 2.

| Signal      | I/O | Pinout | Description                               |

|-------------|-----|--------|-------------------------------------------|

| RTC_TAMPER1 | I   | 18     | Tamper pin input                          |

| RTC_TAMPER2 | I   | NA     | Tamper pin input                          |

|             |     |        | Connects to an external 32.768kHz crystal |

Table 2: RTC signals and pinout on NINA-B50

## 2.5 Serial interfaces

NINA-B50 supports the following serial communication interfaces:

- Two Low Power UART (LPUART) interfaces: 4-wire universal asynchronous receiver/transmitter interface.

- Two Low Power SPI (LPSPI) interfaces: Up to three serial peripheral interfaces can be used simultaneously.

- Two Low Power I2C (LPI2C) interfaces: Inter-Integrated Circuit (I2C) interface for communication with digital sensors.

- Single I3C interface: Based on an enhanced serial communication specification, this interface improves the features, performance, and power efficiency available in I2C. For mid-speed applications, it provides an alternative to the Standard Peripheral Interface (SPI).

- Single programmable FLEXIO: This highly configurable interface is suitable for a wide range of functionalities, including but not limited to UART, I2C, SPI, I2S, Camera IF, Motorola 68K/Intel 8080 bus, PWM/Waveform generation, and input capture for interval measurements using the Single-Edge Nibble Transmission (SENT) protocol, for example.

Including the listed interfaces above, the NINA-B50 automotive grade modules also support the following communication interfaces:

- Single highly configurable, synthesizable Controller Area Network (FlexCAN) interface to be used as a vehicle serial data bus.

- Local Interconnect Network (LIN) capabilities supported via the two LPUART interfaces for communication between components in vehicles.

- The module shares most digital interface pins between digital, and analog interfaces, and GPIOs. By multiplexing the signals, several digital functions can be made available on a single pin.

- Two of the SPI interfaces share common hardware with the I2C interfaces, which means that they can't be used simultaneously. If both I2C interfaces are in use, then only one SPI interface is available.

# 2.5.1 Low Power Universal Asynchronous Receiver/Transmitter (LPUART)

NINA-B50 supports two Low Power Universal Asynchronous Receiver/Transmitter (LPUART) interfaces, LPUART0 and LPUART1.

LPUART interfaces provides asynchronous, serial communication capability with external devices. LPUART supports a non-return-to-zero (NRZ) encoding format and IrDA compatible, low-speed, serial infrared (SIR) format. The LPUART interfaces can continue operating while the processor is in low-power mode – if an appropriate peripheral clock is available. The LPUART can generate an interrupt or DMA request to wake up the module from low power modes.

The LPUART interfaces support hardware flow control and baud rates up to 1 Mbps.

Pin configuration:

- TXD, data output pin

- RXD, data input pin

- RTS, Request To Send, flow control output pin (optional)

- CTS, Clear To Send, flow control input pin (optional)

### 2.5.2 Low-power serial peripheral interface (LPSPI)

NINA-B50 supports two Low-power Serial Peripheral Interface (LPSPI) interfaces, LPSPI0, and LPSPI1.

- LPSPI0 doesn't support a PCS1/HREQ pin and the related fields in the CFGR0 register are reserved.

- LPSPI is a low-power SPI that provides an efficient interface to a SPI bus either as a Main and/or Sub node. The SPI bus is a synchronous serial communication interface commonly used in embedded systems for communications between microcontrollers and peripheral devices over short distances. Low-power serial peripheral interfaces are typically used in Secure Digital cards and LCD displays.

Features of the LPSPI include:

- Pin configuration in main node configuration:

- $\circ$   $\,$  SCK, Serial clock output, up to 12 MHz for LPSPI0 and 24 MHz for LPSPI1  $\,$

- o SOUT, Serial Output data line

- SIN, Serial Input data line

- PCS[0-3], Active-low, Chip select outputs that define which Sub node to communicate with on the bus.

- Pin configuration in sub node configuration:

- SCK, Serial clock input up to 12 MHz

- o SOUT, Serial Output data line

- SIN, Serial Input data line

- $\circ~$  PCS[0-3], Chip select, active-low, inputs that connect/disconnect the Sub-node interface from the bus.

- Supports Main and Sub node on both interfaces. Main node operation supports up to four peripheral Chip selects.

- Continues operating in Sleep modes if configured to do so and an appropriate clock is available

- Minor CPU overhead with DMA offloading of FIFO register accesses.

- Supports DMA accesses and generates a DMA request

- Configurable clock polarity and clock phase

- Enables external memory to connect to the module for use as external storage, including SD cards, LCD displays, and graphic data. If external flash is used, LPSPI1 is configured as the Main mode, using the pin assignments shown in Figure 3.

| Signal name | NINA-B50 pin | Description                           |

|-------------|--------------|---------------------------------------|

| LPSPI1_SCK  | PTB2         | Serial clock output, up to 24 MHz     |

| LPSPI1_SIN  | PTB1         | Serial input data/ Data 1 I/O signal  |

| LPSPI1_SOUT | PTB3         | Serial output data/ Data 0 I/O signal |

| Signal name | NINA-B50 pin | Description                                                                                       |

|-------------|--------------|---------------------------------------------------------------------------------------------------|

| LPSPI1_PCS2 | PTC0         | Data 2 I/O signal                                                                                 |

| LPSPI1_PCS3 | PTC1         | Data 3 I/O signal                                                                                 |

| LPSPI1_PCS0 | PTB0         | Active-low Chip/Sub node select output, Selects which Sub node on the bus is to communicate with. |

Figure 3: Main node configuration for external flash

- By default, SIN is input signal and SOUT is output signal but SIN and SOUT can be configured differently.

- SIN and SOUT instead of commonly used MOSI and MISO are used for SPI data signal names throughout this datasheet to keep the names aligned with the names in the NXP K32W1480 data sheet [3], NXP K32W1480 reference manual [4], NXP KW45 data sheet [5] and NXP KW45 reference manual [6].

### 2.5.3 Low Power Inter-Integrated Circuit (LPI2C)

NINA-B50 supports two Low Power Inter-Integrated Circuit (LPI2C) interfaces, LPI2C0, and LPI2C1. The interfaces provide a synchronous packet-switched, single-ended serial bus that can be used for Main and Sub nodes. It can transfer and/or receive data on a 2-wire bus network and is often used to attach microcontrollers to lower-speed peripheral ICs.

The interfaces comply with the System Management Bus (SMBus) specification (version 3) and can operate as both Main and Sub nodes. The I2C bus supports standard-mode (100 kbps), fast-mode (400 kbps), fast-mode plus (1 Mbps) and ultra-fast (3.2/3.33 Mbps) operation. The interfaces also support multiple Main nodes including synchronization and arbitration. Any number of Main nodes can be present on the LPI2C interface. Additionally, Main and Sub node roles may change between messages (after a STOP is sent).

DMA offloading of FIFO register accesses mean that use of the interfaces operate with only a minor CPU overhead. The interfaces continue to operate in sleep modes if an appropriate clock is available.

- The I2C 2-wire pin configuration:

- SCL, clock output in Main mode, input in Sub mode

- $\circ$  SDA, data input/output pin

- The I2C 4-wire pin configuration:

- SCL, clock input pin

- SDA, data input pin

- SCLS, secondary clock line. SCLS output pin in Main mode. If LPI2C Main/Sub nodes are configured to use separate pins, then this is the SCL pin for the Main node.

- SDAS, secondary data line. SDAS output pin in Main mode. If LPI2C Main/Sub nodes are configured to use separate pins, then this is the SDA pin for the Sub node.

### 2.5.4 Improved Inter-Integrated Circuit (I3C)

NINA-B50 supports a single Improved Inter-Integrated Circuit (I3C) interface, I3C0. Based on an enhanced serial communication specification developed by the Mobile Industry Processor Interface Alliance (MIPI Alliance), this interface improves the features, performance, and power efficiency available in I2C. For mid-speed applications, it provides an alternative to the Standard Peripheral Interface (SPI). The I3C bus is intended to connect microcontrollers (MCU) and application processors (AP) to sensors, actuators, and other MCUs as Sub nodes.

The major use cases for this interface include:

- Connecting an MCU to other MCUs, and

- Connecting an Access Point (AP) to an MCU

To operate in I3C mode, the PV, PE, and PS values in the corresponding PORT\_PCR registers must be correctly configured with a pull-up resistor.

Features of the I3C interface include:

- 2-wire multi-drop bus capable of 12 MHz clock speeds for up to 11 devices.

- In-band interrupts (IBI) are allowed, which allow Sub nodes to notify Main nodes.

- Built-in commands are issued in a separate "space," so that these commands do not collide with normal messaging between the Main and Sub nodes.

- Organized forms of multiple main nodes modes. Secondary Main nodes can use clean handoffs between other Main nodes.

- Devices can hot-join the bus later than when the bus starts.

- Capable of using both I2C and I3C busses with bridging support for to I2C, SPI, UART, and other busses.

- Higher data rate modes (about 20 Mbps) are optionally available.

- Sub nodes can be as small as 2K gates (or less), which allows the I3C interface to be controlled by a processor and fully state-machine driven.

- Supports the full I3C feature set except for ternary data rates (HDR-TSP, HDR-TSL).

### 2.5.5 Flexible input/output (FlexIO)

NINA-B50 supports a single FlexIO interface, FLEXIO0. This highly configurable interface is suitable for a wide range of functionalities, including but not limited to:

- UART

- I2C

- SPI

- I2S

- Camera IF

- Motorola 68K/Intel 8080 bus

- PWM/Waveform generation

Input capture for interval measurements using the Single-Edge Nibble Transmission (SENT) protocol, for example.

Features of the FlexIO include:

- Emulation of a variety of serial/parallel communication protocols

- 32-bit, shift register array with support for transmit, receive, data match, logic mode, and state modes

- Double-buffered, shifter operation for continuous data transfer

- Shifter concatenation to support large transfer sizes

- Automatic start/stop bit generation

- 1, 2, 4, 8, 16, or 32 multi-bit shift widths for parallel interface support

- Interrupt, DMA or polled transmit/receive operation

- Programmable baud rates independent of bus clock frequency, with support for asynchronous operation during stop modes

- Highly flexible 16-bit timers with support for a variety of internal or external trigger, reset, enable and disable conditions

- Programmable logic mode for integrating external digital logic operations, including on-chip or combining pin/shifter/timer functions to generate complex outputs

- Programmable state machine for offloading basic system control functions from CPU, with support for up to eight states, eight outputs, and three selectable inputs per state

- Integrated, general-purpose, input/output registers and pin rising/falling edge interrupts to simplify software support

- Flexible 16-bit timers with support for a variety of trigger, reset, enable and disable conditions

- Programmable logic blocks allowing the implementation of digital logic functions on-chip and configurable interaction of internal and external modules

- Programmable state machine for offloading basic system control functions from CPU

## 2.5.6 FlexCAN

The FlexCAN interface on the NINA-B50 automotive grade modules is a full implementation of the CAN protocol specification, the CAN with Flexible Data Rate (CAN FD) protocol, and the CAN 2.0 version B protocol, which supports both standard and extended message frames and long payloads.

The CAN interfaces includes the following features:

- Compliant with the ISO 11898-1:2015 standard

- Flexible mailboxes configurable to store 0 to 8, 16, 32, or 64 bytes data length

- Each mailbox configurable as receive or transmit, supporting standard and extended messages

- Individual Rx Mask registers per mailbox

- Full-featured legacy Rx FIFO with storage capacity for up to six frames and automatic internal pointer handling with DMA support

- Full-featured enhanced Rx FIFO with storage capacity for up to 12 CAN FD frames and automatic internal pointer handling with DMA support

- Transmission abort capability

- Total 32 Flexible message buffers (MBs) configurable as Rx or Tx with 8 bytes data length of each

- RAM not used by reception or transmission structures can be used as general-purpose RAM space

- Listen-Only mode capability

- Programmable Loop-Back mode supporting self-test operation

- Programmable transmission priority scheme: lowest ID, lowest buffer number, or highest priority fist

- Time stamp based on 16-bit free running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independence from the transmission medium (an external transceiver is assumed)

- Short latency time due to an arbitration scheme for high-priority messages

- Low power modes, with programmable wakeup on bus activity or matching with received frames (Pretended Networking)

- Transceiver delay compensation feature when transmitting CAN FD messages at faster data rates

- Remote request frames may be managed automatically or by software

- CAN bit time settings and configuration bits can only be written in Freeze mode

- Tx mailbox status (Lowest priority buffer or empty buffer)

- Identifier Acceptance Filter Hit Indicator (IDHIT) register for received frames

- SYNCH bit available in Error in Status 1 register to indicate that the module is synchronous with CAN bus

- CRC status for transmitted message

- Legacy Rx FIFO Global Mask register

- Selectable priority between mailboxes and Rx FIFO during matching process

- Powerful legacy Rx FIFO ID filtering, capable of matching incoming IDs against either 128 extended, 256 standard, or 512 partial (8 bit) IDs, with up to 32 individual masking capability

- Powerful Enhanced Rx FIFO ID filtering, capable of matching incoming IDs against either 16 extended or 32 standard ID filter elements with three filtering schemes: mask + filter, range, and two filters without mask.

- 100% backward compatibility with previous FlexCAN version

- Supports Pretended Networking functionality in low power: Doze mode, Stop mode

- A CAN transceiver needs to be connected to the CAN interface of the NINA-B50 automotive grade module to support the CAN feature.

- CAN interface is supported on the NINA-B50 automotive grade modules but not supported on the NINA-B50 professional grade modules.

## 2.5.7 LIN

The single-wire LIN bus is a communication standard to complement high-end automotive buses like CAN, with lower-cost solutions where less performance suffices.

The LIN features are supported by the NINA-B50 automotive grade modules by connecting a LIN transceiver to one of the two LPUART interfaces of the module.

**37** L

LIN is supported on the NINA-B50 automotive grade module but not supported on the NINA-B50 professional grade module.

## 2.6 Other digital interfaces

## 2.6.1 Timer/ PWM (TPM)

NINA-B50 modules support three Pulse Width Modulation timers, TPM0, TPM1 and TPM2. TPM0 is a 2-channel 32-bit timer and TPM1 and TPM2 are 6-channel 32-bit timers.

The Pulse Width Modulation timer (TPM) supports input capture, output compare, and the generation of Pulse Width Modulation (PWM) signals to control electric motor and power management applications. The counter, compare, and capture registers are clocked by an asynchronous clock that can remain enabled in low power modes.

Features of TPM include:

- Selectable clock mode. In this mode the timer can be incremented on every edge of the asynchronous clock or on the rising edge of an external clock input synchronized to the asynchronous counter clock

- Pre-scaler allows the timer to divide-by 1, 2, 4, 8, 16, 32, 64, or 128

- 32-bit counter that operates as a free-running or modulo counter. The counting can be both up or up-down

- Six configurable channels for input capture, output compare, edge-aligned or centeraligned PWM modes

- Interrupts and/or DMA requests per channel and on counter overflow conditions

- Selectable trigger input to optionally reset, start, increment, or stop the counter in overflow conditions

- Generation of hardware triggers per channel when the counter overflows

### 2.6.2 Quadrature Decoder (QDEC)

The quadrature decoder (QDEC) is used to read quadrature encoded data from mechanical and optical sensors in the form of digital waveforms. Quadrature encoded data is often used to indicate rotation of a mechanical shaft in either a positive or negative direction.

The QDEC uses two inputs, **channel 0** (**PHASE\_A**) and **channel 1** (**PHASE\_B**), to control incremental and decremental counting in the TPM counter. The QDEC supports two encoding modes: count and direction encoding mode and phase encoding mode. See also Timer/ PWM (TPM).

## 2.7 Analog interface

14 out of the 29 digital GPIOs can be multiplexed to analog functions. The following analog functions are available:

- 1x 16-bit Analog to Digital Converter (ADC)

- 2x Low-power Comparator (LPCMP)

- 1x Voltage Reference (VREF)

### 2.7.1 Analog to Digital Converter (ADC)

A 16-bit dual successive approximation Analog to Digital Converter (ADC) is used to sample an analog voltage on any of the analog-capable pins on the module.

Features of the ADC include:

- Full swing input range of 0 V to VCC\_IO

- Supports three sampling modes:

- Single-ended mode: Only one side channel from A-side or B-side is converted.

- Differential mode: A single input pin is used.

- Dual single-ended mode: Both A-side and B-side channels are converted independently and simultaneously. In this case, fixed pairs of input pins are used. For example, ADC0\_A5 and ADC0\_B5 or ADC0\_A6 and ADC0\_B6.

- Resolution:

- Differential mode: 16-bit high resolution or 13-bit standard resolution

- Single-ended mode: 16-bit high resolution or 12-bit standard resolution

- Sample rates up to 2 MS/s

- Configurable analog input sample time

- Configurable speed options to accommodate operation in low-power modes

- Trigger detection with up to four trigger sources with priority level configuration

- Multiple command buffers provide flexibility for channel scanning and independent channel selections for different trigger sources.

- Automatic comparison of conversion results

- Two independent FIFO result registers, each containing 16 entries

- Interrupt, DMA, or polled operation

- Linearity and Gain adjustment calibration logic

### 2.7.2 Low Power Comparator (LPCMP)

NINA-B50 supports two Low Power Comparators, (LPCMP), LPCMP0, and LPCMP1.

The comparators provide circuits for comparing two analog input voltages on the analogenabled pins on the module. The comparators are comprised of a comparator (CMP), DAC, and analog mux (ANMUX).

Features of the comparator include:

- Operation over the full input range of 0 V to VCC\_IO

- Multiple operation modes with advanced features to produce a wide range of outputs, such as sampled, windowed, and digitally filtered.

- Selectable performance levels: nano power mode, low power/speed mode, and high power/speed mode

- Supports interrupt and DMA, programmable hysteresis control, and selectable inversion on comparator output

- Two 8-to-1 channel ANMUX that can operate over the full range of the supply voltage to select input signal from eight channels

- 8-bit resolution DAC with a 256-tap resistor, ladder network that provides selectable supply reference source, selectable reference voltage, and configurable low power/speed mode or high power/speed mode

## 2.7.3 Voltage Reference (VREF)

NINA-B50 series modules have one Voltage Reference (VREF) buffer system that employs unity gain amplifiers.

For use with external devices, VREF provides reference voltage that can be set from 1.0 V to 2.1 V. The buffered reference is also available internally for use with on-module analog peripherals, such as the ADC, DAC, or CMP. VREF has a dedicated output pin, **VREFO**. When VREF is enabled, the reference voltage is placed on the **VREFO** pin.

The voltage reference has three operating modes yield different levels of supply rejection and power consumption. The operating modes are OFF mode, low-power buffer mode, and high-power buffer mode.

- In the OFF mode, the VREF bandgap and the output buffers are disabled, which means that the voltage output is not buffered.

- In low power buffer mode, the module activates the buffer to generate a buffered voltage for **VREF\_OUT.** This voltage can be adjusted within the range of 1.0 V to 2.1 V.

- In high-power buffer mode, the module activates the high-power buffer to generate a programmable buffered voltage for **VREF\_OUT**. The voltage can be adjusted in 0.1 V increments ranging from 1.0 V to 2.1 V. The reference voltage output can be fine-tuned with 0.5 mV increments. For course tuning adjust the output with 100 mV resolution using the trim registers.

The VREF system includes an internal voltage regulator that you can enable to enhance supply noise rejection, as well as an internal oscillator that provides the chop clock. For optimal VREF performance, it is advisable to enable the regulator and oscillator whenever possible. If you are using the chop function, you must also enable the internal voltage regulator. When enabling the internal regulator, a specific sequence should be followed.

VREF can operate when the chip is in a low-power mode. However, enabling the VREF regulator results in increased current consumption. In low power mode, it may be appropriate to disable the VREF regulator to minimize current consumption. Disabling the VREF regulator can lead to a reduction in the accuracy of the output voltage, by as much as several millivolts (mV).

### 2.7.4 Analog pin options

An analog pin may not be simultaneously used for multiple functions.

Table 3 shows the supported connections of the analog functions.

| Symbol | Analog function                                 | Can be connected to                                            |

|--------|-------------------------------------------------|----------------------------------------------------------------|

| VCC_IO | Analog domain power supply                      | VCC or VOUT_SWITCH                                             |

| ADCP   | ADC single-ended or differential positive input | Any analog input on A-side (ADC0_An) or on<br>B-side (ADC0_Bn) |

| ADCN   | ADC differential negative input                 | Any analog pin of ADC0_An and ADC0_Bn pin pairs                |

| VREFH  | Reference voltage for the CMP-DAC               | Can be configured to be VCC_IO or VREFO                        |

| LP_INP | Low-power comparator IN+                        | Any analog pin CMPn_INx                                        |

| LP_INM | Low-power comparator IN-                        | Any analog pin CMPn_INx                                        |

| LPCMPO | Low-power comparator output                     | CMP0_OUT or CMP1_OUT                                           |

Table 3: Possible uses of the analog pins

## 2.8 GPIO

NINA-B50 supports four General-Purpose Input and Output (GPIO) interfaces: GPIOA, GPIOB, GPIOC, and GPIOD. Two interrupt channels have been assigned to each GPIO interface.

For optimal pin performance, the GPIO interfaces communicate with the processor core through a zero-wait state interface.

The module has 29 GPIO pins. 14 of these are analog-capable pins that can be assigned to analog functions. The signal multiplexing of each pin is shown in Table 5.

### 2.8.1 Drive strength

All GPIO pins are configured for low current consumption by default. Using this standard drive strength, a pin configured as output can source or sink a specific amount of current.

If the timing requirements of a digital interface can't be met, or if an LED requires more current, a high drive strength mode is also available. This mode allows the digital output to draw more current. See also Digital pins.

## 2.9 Debug interfaces

### 2.9.1 SWD

NINA-B50 supports a single external Serial Wire Debug (SWD) interface for debugging and testing. The SWD interface consists of two pins: the clock pin, **SWDCLK**, and the single bidirectional data pin, **SWDIO**.

### 2.9.2 DAP

NINA-B50 supports a Debug Access Port (DAP) to debug and trace the core system of the module. DAP is a standard Arm CoreSight component. The DAP allows real-time access to the module registers from an external debugger without halting the processor cores. The DAP provides multiple, Main node, driving ports. All ports are accessible and controlled through a single external interface port to provide system-wide debug. On NINA-B50, the SWD interface is used as the external connection interface of DAP.

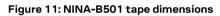

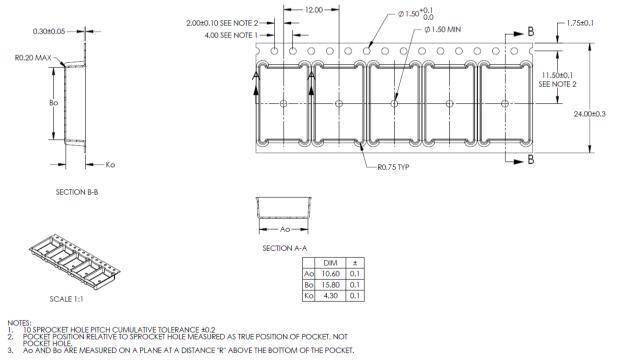

### 2.9.3 SWO