# **SARA-N3** series

### Multi-band NB-IoT (LTE Cat NB2) modules

Data sheet

#### Abstract

Technical data sheet describing SARA-N3 Narrowband Internet of Things cellular modules. These modules are a complete and cost-efficient solution offering multi-band data transmission for the Internet of Things technology in a compact form factor.

www.u-blox.com

## **Document information**

| Title                         | SARA-N3 series               |              |

|-------------------------------|------------------------------|--------------|

| Subtitle                      | Multi-band NB-loT (LTE Cat N | NB2) modules |

| Document type                 | Data sheet                   |              |

| Document number               | UBX-18066692                 |              |

| Revision and date             | R11                          | 27-Sep-2022  |

| <b>Disclosure restriction</b> | C1-Public                    |              |

| Product status                   | Corresponding content status |                                                                                        |  |  |  |  |  |

|----------------------------------|------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|

| Functional sample                | Draft                        | For functional testing. Revised and supplementary data will be published later.        |  |  |  |  |  |

| In development /<br>prototype    | Objective specification      | Target values. Revised and supplementary data will be published later.                 |  |  |  |  |  |

| Engineering sample               | Advance information          | Data based on early testing. Revised and supplementary data will be published later.   |  |  |  |  |  |

| Initial production               | Early prod. information      | Data from product verification. Revised and supplementary data may be published later. |  |  |  |  |  |

| Mass production /<br>End of life | Production information       | Final product specification.                                                           |  |  |  |  |  |

#### This document applies to the following products:

| Product name | Type number      | Modem version | Application version | PCN reference | Product status  |

|--------------|------------------|---------------|---------------------|---------------|-----------------|

| SARA-N310    | SARA-N310-00X-00 | 18.13         | A01.01              | UBX-21017614  | End of life     |

|              | SARA-N310-00X-01 | 18.13         | A01.02              | UBX-21039338  | End of life     |

|              | SARA-N310-00X-02 | 18.13         | A01.03              | UBX-22003602  | End of life     |

|              | SARA-N310-00X-03 | 18.13         | A01.04              | UBX-22023924  | Mass production |

u-blox or third parties may hold intellectual property rights in the products, names, logos and designs included in this document. Copying, reproduction, modification or disclosure to third parties of this document or any part thereof is only permitted with the express written permission of u-blox.

The information contained herein is provided "as is" and u-blox assumes no liability for its use. No warranty, either express or implied, is given, including but not limited to, with respect to the accuracy, correctness, reliability and fitness for a particular purpose of the information. This document may be revised by u-blox at any time without notice. For the most recent documents, visit www.u-blox.com.

Copyright © u-blox AG.

## Contents

| Document information                                                   | 2  |

|------------------------------------------------------------------------|----|

| Contents                                                               | 3  |

| 1 Functional description                                               | 5  |

| 1.1 Overview                                                           | 5  |

| 1.2 Product features                                                   | 5  |

| 1.3 Block diagram                                                      | 6  |

| 1.4 Product description                                                | 6  |

| 1.5 AT command support                                                 | 7  |

| 1.6 Supported features                                                 | 7  |

| 2 Interfaces                                                           | 9  |

| 2.1 Power management                                                   |    |

| 2.1.1 Module supply input (VCC)                                        |    |

| 2.1.2 RTC supply input/output (V_BCKP)                                 |    |

| 2.1.3 Digital I/O interfaces supply output (V_INT)                     | 9  |

| 2.2 Antenna                                                            |    |

| 2.2.1 Cellular antenna RF interface (ANT)                              |    |

| 2.2.2 Bluetooth antenna RF interface (ANT_BT)                          |    |

| 2.2.3 Antenna detection (ANT_DET)                                      |    |

| 2.3 System functions                                                   |    |

| 2.3.1 Module power-on                                                  |    |

| 2.3.2 Module power-off                                                 |    |

| 2.3.3 Module reset                                                     |    |

| 2.3.4 Digital I/O interfaces voltage selection (VSEL)                  |    |

| 2.4 SIM interface                                                      |    |

| 2.5 Serial interfaces                                                  |    |

| 2.5.1 Main primary serial interface (UART)                             |    |

| 2.5.2 Secondary auxiliary serial interface (UART AUX)                  |    |

| 2.5.3 Additional serial interface for FW upgrade and Tracing (UART FT) |    |

| 2.5.4 DDC (I2C) interface                                              |    |

| 2.6 ADC                                                                |    |

| 2.7 GPIO                                                               |    |

| 3 Pin definition                                                       |    |

| 3.1 Pin assignment                                                     |    |

| 4 Electrical specification                                             |    |

| 4.1 Absolute maximum rating                                            |    |

| 4.1.1 Maximum ESD                                                      |    |

| 4.2 Operating conditions                                               |    |

| 4.2.1 Operating temperature range                                      |    |

| 4.2.2 Supply/power pins                                                |    |

| 4.2.3 Current consumption                                              |    |

| 4.2.4 RF characteristics                                               |    |

| 4.2.5 PWR_ON pin                                                       | 22 |

| 4.2.6 RESET_N p       | in                     |

|-----------------------|------------------------|

| 4.2.7 SIM interfa     | ce pins                |

| 4.2.8 Generic Dig     | ital Interface pins 23 |

| 4.2.9 ADC pins        |                        |

| 5 Mechanical spec     | ifications             |

| 6 Qualification and   | d approvals            |

| 6.1 Reliability tests |                        |

| 6.2 Approvals         |                        |

| 6.2.1 ATEX certif     | -<br>Fication          |

| 7 Product handling    | g                      |

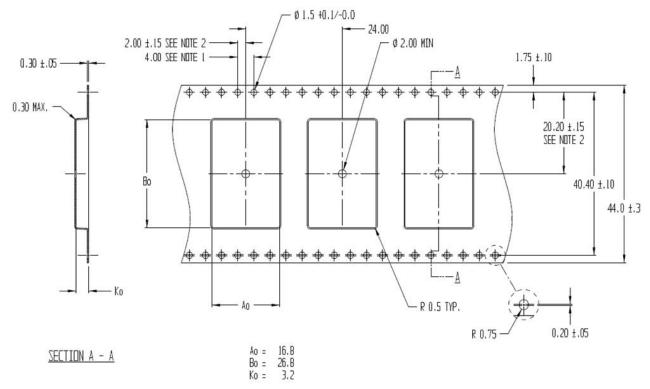

| 7.1 Packaging         |                        |

| 7.1.1 Reels           |                        |

| 7.1.2 Tapes           |                        |

| 7.2 Moisture Sensit   | ivity Levels           |

| 7.3 Reflow soldering  | g                      |

| 7.4 ESD precaution    | s                      |

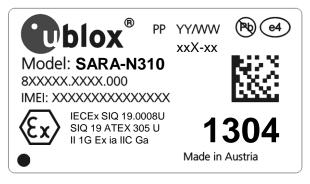

| 8 Labeling and ord    | lering information     |

| 8.1 Product labeling  | J                      |

| 8.2 Explanation of c  | odes                   |

| 8.3 Ordering codes.   |                        |

| Appendix              |                        |

| A Glossary            |                        |

| Related documenta     | tion                   |

| Revision history      |                        |

| •                     |                        |

## **1** Functional description

### 1.1 Overview

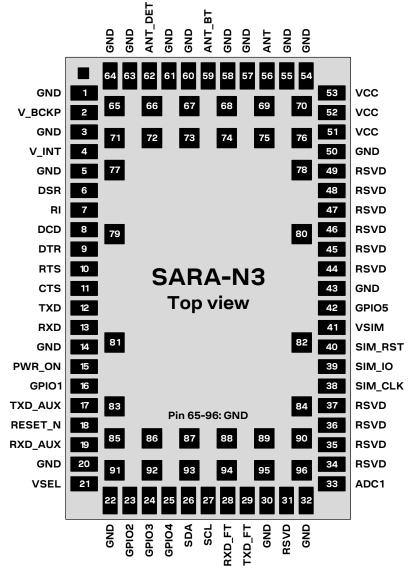

The SARA-N3 series are multi-band NB-IoT (LTE Cat NB2) modules supporting a preliminary set of features based on 3GPP release 14 in the miniature SARA LGA form factor (16.0 x 26.0 mm, 96-pin).

The modules offer multi-band NB-IoT data communication enabling multi-regional coverage over an extended operating temperature range of -40 °C to +85 °C, with extremely low power consumption.

The SARA-N3 series modules introduce several new functionalities for NB-IoT products, including features like TCP, DTLS, LwM2M, MQTT, MQTT-SN, SSL/TLS, HTTP(S). They enable a diverse and broad set of new IoT applications and simplify customer migration to NB-IoT from other cellular or unlicensed technologies. u-blox nested design eases migration between other u-blox LTE, 3G and 2G modules, while enabling future-proof, seamless scalability across technologies.

Critical firmware updates can be delivered over the air using the u-blox uFOTA client / server solution with LwM2M, which is a more lightweight solution compared to OMA-DM.

The SARA-N3 series modules are the optimal choice for IoT devices designed to operate in locations with a very limited coverage and requiring low energy consumption to permit a very long operating life of the primary batteries. Examples of applications include and are not limited to smart grids, smart metering, telematics, street lighting, environmental monitoring and control, security and asset tracking.

| Module    | Region | С                     | ellula            | r RAT                  |       | Ir  | nter      | face | s    |       |                    |                 |      |                                |                        | Fe                           | atuı                         | res                |                        |                         |           |                          |                               | G        | Grad         | е          |

|-----------|--------|-----------------------|-------------------|------------------------|-------|-----|-----------|------|------|-------|--------------------|-----------------|------|--------------------------------|------------------------|------------------------------|------------------------------|--------------------|------------------------|-------------------------|-----------|--------------------------|-------------------------------|----------|--------------|------------|

|           |        | 3GPP release baseline | 3GPP LTE category | LTE FDD bands          | UARTs | USB | DDC (I2C) | USIM | ADCs | GPIOs | Antenna supervisor | Power Save Mode | eDRX | Bluetooth 4.2 (BR/EDR and BLE) | Embedded TCP/UDP stack | Embedded CoAP, MQTT, MQTT-SN | Embedded HTTP, FTP, PPP, DNS | Embedded TLS, DTLS | Dual stack IPv4 / IPv6 | LwM2M Device Management | Last gasp | FW update over AT (FOAT) | FW update over the air (FOTA) | Standard | Professional | Automotive |

| SARA-N310 | Global | 14                    | NB2               | 3, 5, 8<br>20, 28<br>★ | •     |     | 0         | •    | •    | •     | •                  | •               | •    | 0                              | •                      | •                            | •                            | •                  | •                      | •                       | •         | •                        | •                             |          | •            |            |

### 1.2 Product features

Table 1: SARA-N3 series main features summary

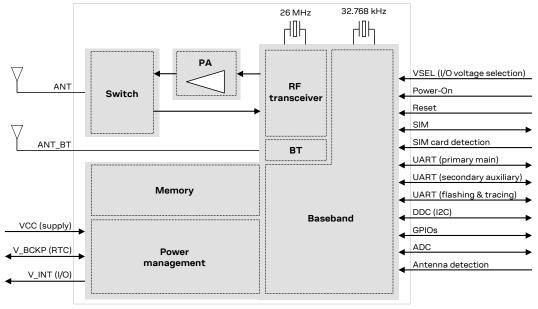

### 1.3 Block diagram

Figure 1: SARA-N3 series block diagram

- The "00" product versions of SARA-N3 series modules do not support the following interfaces, which should not be driven by external devices:

- Bluetooth interface (ANT\_BT)

- Secondary auxiliary serial interface (UART AUX)

- SPI interface

- DDC (I2C) interface

### 1.4 Product description

| Item                    | SARA-N310 <sup>1</sup>        |

|-------------------------|-------------------------------|

| Protocol stack          | 3GPP release 14 <sup>2</sup>  |

| Radio Access Technology | LTE category NB2 Half-Duplex  |

| Operating bands         | Band 3 (1800 MHz)             |

|                         | Band 5 (850 MHz)              |

|                         | Band 8 (900 MHz)              |

|                         | Band 20 (800 MHz)             |

|                         | Band 28 (700 MHz)             |

| Deployment modes        | In-Band                       |

|                         | Guard-Band                    |

|                         | Standalone                    |

| Power class             | Class 3 (23 dBm) <sup>3</sup> |

| Sustained data rate     | LTE category NB2:             |

|                         | Up to 140 kb/s UL             |

|                         | Up to 125 kb/s DL             |

Table 2: SARA-N3 series NB-IoT characteristics summary

<sup>&</sup>lt;sup>1</sup> Additional LTE bands (1, 2, 4, 12, 13, 18, 19, 26, 66, 71, 85) available in future FW versions

<sup>&</sup>lt;sup>2</sup> Key subset of features

<sup>&</sup>lt;sup>3</sup> Configurable to other power class by AT command

### 1.5 AT command support

The SARA-N3 series modules support AT commands according to the 3GPP standards, plus the u-blox AT command extensions.

3

For the complete list of all supported AT commands and their syntax description, see the SARA-N2 / SARA-N3 series AT commands manual [1].

### 1.6 Supported features

Table 3 lists some of the features supported by SARA-N3 series modules.

| Feature                                        | Description                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Network indication                             | Pin configured to indicate the network status: registered home network, registered roaming, data call enabled, no service. The feature can be enabled through the +UGPIOC AT command.                                                                                                                                                                                     |

| Antenna detection                              | The <b>ANT_DET</b> pin provides antenna presence detection capability, evaluating the resistance from the <b>ANT</b> pin to GND by means of an external antenna detection circuit implemented on the application board. The feature can be enabled through the +UANTR AT command.                                                                                         |

| Jamming detection                              | Detects "artificial" interference that obscures the operator's carriers providing access to the NB-<br>loT service and reports the start and stop of such conditions to the application processor (AP).<br>The AP can react appropriately, e.g. by switching off the radio transceiver to reduce power<br>consumption and monitoring the environment at constant periods. |

| Dual stack IPv4/IPv6                           | Capability to move between IPv4 and IPv6, dual stack network infrastructures IPv4 and IPv6 addresses can be used.                                                                                                                                                                                                                                                         |

| TCP/UDP                                        | Embedded TCP/IP and UDP/IP stack, to establish a transparent end-to-end communication through TCP or UDP sockets via serial interface.                                                                                                                                                                                                                                    |

| DTLS (v1.2)                                    | Embedded Datagram Transport Layer Security (DTLS) provides security for CoAP, LwM2M, MQTT-SN and UDP communications.                                                                                                                                                                                                                                                      |

| CoAP (RFC 7252 [5])                            | Embedded Constrained Application Protocol (CoAP) datagram-based client/server application protocol designed to easily translate from HTTP for simplified integration with the web.                                                                                                                                                                                        |

| SSL/TLS (v1.0, v1.1, v1.2)                     | Transport Layer Security (TLS) provides security for HTTP, MQTT and TCP communications.                                                                                                                                                                                                                                                                                   |

| MQTT (v3.1.1) and<br>MQTT-SN (v1.2)            | Embedded Message Queuing Telemetry Transport (MQTT) and MQTT for Sensor Networks (MQTT-SN) publish-subscribe messaging protocols designed for lightweight M2M communications over TCP (MQTT) or over UDP (MQTT-SN). These allow one-to-one, one-to-many and many-to-one communications over a TCP or UDP connection.                                                      |

| FTP                                            | Embedded File Transfer Protocol functionality is supported via AT commands.                                                                                                                                                                                                                                                                                               |

| HTTP and HTTPS<br>(v1.0, v1.1)                 | Embedded Hyper-Text Transfer Protocol as well as embedded Secure Hyper-Text Transfer<br>Protocol functionalities are supported via AT commands.                                                                                                                                                                                                                           |

| Release Assistance                             | The Release Assistance feature introduced in 3GPP release 13 allows the module to request for the RRC connection to be dropped as soon as the message has been received by the network. This feature allows a reduction in the module power consumption.                                                                                                                  |

| Firmware update Over AT commands (FOAT)        | Firmware module update over AT command interface.<br>The feature can be enabled and configured through the +UFWUPD AT command.                                                                                                                                                                                                                                            |

| u-blox Firmware update<br>Over The Air (uFOTA) | u-blox firmware update over the LTE air interface client/server solution using LwM2M (v1.0).                                                                                                                                                                                                                                                                              |

| RPM                                            | The Radio Policy Manager (RPM) feature allows a reduction in the module power consumption as the module does not retry an unnecessary service request.                                                                                                                                                                                                                    |

| Last gasp                                      | In case of power supply outage (i.e. main supply interruption, battery removal, battery voltage<br>below a certain threshold) the cellular module can be configured to send an alarm notification to a<br>remote entity.<br>The feature can be enabled and configured through the +ULGASP AT command.                                                                     |

| Feature                 | Description                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Power Saving Mode (PSM) | The Power Saving Mode (PSM) feature, defined in 3GPP release 13, allows further reduction of the module current consumption maximizing the amount of time a device can remain in extremely low power deep sleep mode during periods of data inactivity. It can be activated and configured by the +CPSMS AT command.     |  |  |  |  |

| Deep-sleep mode         | The SARA-N3 series modules enters in extremely low power deep sleep mode whenever possible, using the internal 32 kHz clock to maintaining an extremely low current consumption. This optimizes the lifetime of the battery pack used to supply the system.                                                              |  |  |  |  |

| eDRX                    | Extended mode DRX, based on 3GPP release 13, reduces the amount of signaling overhead decreasing the frequency of scheduled measurements and/or transmissions performed by the module. This in turn leads to a reduction in the module power consumption while maintaining a perpetual connection with the base station. |  |  |  |  |

| Coverage Enhancement    | Coverage Enhancements modes introduced in 3GPP release 13 for the NB-loT system improve the cell signal penetration allowing a 20 dB coverage enhancement over standard GSM systems.                                                                                                                                     |  |  |  |  |

| Mobility Enhancement    | Mobility Enhancements introduced in 3GPP release 14 for the NB-loT system.                                                                                                                                                                                                                                               |  |  |  |  |

Table 3: Main features of SARA-N3 series modules

## 2 Interfaces

### 2.1 Power management

### 2.1.1 Module supply input (VCC)

SARA-N3 series modules must be supplied through the three **VCC** pins by a proper DC power supply. Voltage must be stable during module operation, taking into account that the current drawn through the **VCC** pins may vary significantly based on the power consumption profile of the NB-IoT system.

### 2.1.2 RTC supply input/output (V\_BCKP)

**V\_BCKP** is the Real Time Clock (RTC) supply of SARA-N3 series modules. When **VCC** voltage is within the valid operating range, the internal Power Management Unit (PMU) supplies the RTC and the same supply voltage is available on the **V\_BCKP** pin. If the **VCC** voltage is under the minimum operating limit (e.g. during not powered mode), the RTC can be externally supplied through the **V\_BCKP** pin.

### 2.1.3 Digital I/O interfaces supply output (V\_INT)

SARA-N3 series modules provide supply rail output on the **V\_INT** pin, which is used internally to supply the digital I/O interfaces of the modules (UART interfaces, I2C interface, and GPIO pins).

The **V\_INT** operating voltage can be selected using the **VSEL** input pin:

- If the **VSEL** input pin is connected to GND, the digital I/O interfaces operate at 1.8 V

- If the **VSEL** input pin is left unconnected, the digital I/O interfaces operate at 2.8 V

The **V\_INT** supply output is internally generated when the module is switched on, outside PSM.

- If the VSEL input pin is left unconnected, the VCC voltage shall be inside normal operating range to let the digital I/O interfaces work correctly (see section 4.2.2).

- **Provide a test point connected to the V\_INT** pin for diagnostic purpose.

### 2.2 Antenna

#### 2.2.1 Cellular antenna RF interface (ANT)

The **ANT** pin has an impedance of 50  $\Omega$  and provides the LTE Cat NB2 (NB-IoT) RF interface of the SARA-N3 series modules, to be connected to a proper external cellular antenna.

### 2.2.2 Bluetooth antenna RF interface (ANT\_BT)

The **ANT\_BT** pin has an impedance of 50  $\Omega$  and provides the Bluetooth RF antenna interface of the SARA-N3 series modules.

The Bluetooth functionality is not supported by "00" product versions of SARA-N3 series modules.

The ANT\_BT pin can be left unconnected or it can also be connected to GND.

### 2.2.3 Antenna detection (ANT\_DET)

The **ANT\_DET** pin is an Analog to Digital Converter (ADC) input to sense the antenna presence (as optional feature), evaluating the resistance from the **ANT** pin to GND by means of an external antenna detection circuit implemented on the application board.

### 2.3 System functions

#### 2.3.1 Module power-on

When the SARA-N3 series modules are in the not-powered mode (i.e. switched off with the **VCC** module supply not applied), the switch on routine of the module can be triggered by:

- Applying a VCC supply within the normal operating range of the module (see section 4.2.2), and then forcing a low level on the **PWR\_ON** input pin (normally high due to internal pull-up) for a valid time period (see section 4.2.5).

- Alternately, the **RESET\_N** pin can be held low during the **VCC** rising edge, so that the module switches on by releasing the **RESET\_N** pin when the **VCC** voltage stabilizes at its nominal value within the normal range.

When the SARA-N3 series modules are in power off mode (i.e. switched off, with valid **VCC** supply applied), the switch on routine of the module can be triggered by:

• Forcing a low level on the **PWR\_ON** input pin (normally high due to internal pull-up) for a valid time period (see section 4.2.5).

When the SARA-N3 series modules are in the deep sleep mode (i.e. in Power Saving Mode defined in 3GPP Rel. 13, with valid **VCC** supply applied), the wake-up routine of the module can be triggered by:

- Forcing a low level on the **PWR\_ON** input pin (normally high due to internal pull-up) for a valid time period (see section 4.2.5).

- **Provide a test point connected to the PWR\_ON** pin for diagnostic purposes.

#### 2.3.2 Module power-off

SARA-N3 series modules can be properly switched off, with storage of current parameter settings in the module's non-volatile memory and clean network detach, by:

- AT+CPWROFF command (see the SARA-N2 / SARA-N3 series AT commands manual [1]).

- Low level on the **PWR\_ON** input pin, i.e. forcing the pin (normally high due to internal pull-up) to a low level for a valid time period (see section 4.2.5).

An abrupt under-voltage shutdown occurs on SARA-N3 series modules when the **VCC** supply drops below the extended operating range minimum limit (see section 4.2.2), but in this case it is not possible to perform the storing of the current parameter settings in the module's non-volatile memory as well as a clean network detach.

### 2.3.3 Module reset

SARA-N3 series modules can be properly reset (rebooted), with storage of current parameter settings in the module's non-volatile memory and clean network detach, by:

• AT+CFUN command (see the SARA-N2 / SARA-N3 series AT commands manual [1]), triggering an "internal" or "software" reset / re-boot of the module

An abrupt hardware reset occurs on SARA-N3 series modules when a low voltage level is applied at the **RESET\_N** input pin, which is normally set high by an internal pull-up, for a valid time period (see the section 4.2.6), triggering an "external" or "hardware" reset / re-boot of the module. In this case it is not possible to perform the storing of the current parameter settings in the module's non-volatile memory as well as a clean network detach. The **RESET\_N** line is intended to be driven by open drain, open collector or contact switch.

**Provide a test point connected to the RESET\_N** pin for diagnostic purposes.

### 2.3.4 Digital I/O interfaces voltage selection (VSEL)

The digital I/O interfaces of SARA-N3 series modules (the UARTs, I2C, and GPIOs pins) operate at the **V\_INT** voltage, which can be set to 1.8 V or 2.8 V using the **VSEL** input:

- If the VSEL input pin is connected to GND, the digital I/O interfaces operate at 1.8 V

- If the **VSEL** input pin is left unconnected, the digital I/O interfaces operate at 2.8 V

The operating voltage cannot be changed dynamically: the **VSEL** input pin configuration has to be set before the boot of SARA-N3 series modules and then it cannot be changed after switched on.

If the VSEL input pin is left unconnected, the VCC voltage shall be inside normal operating range to let the digital I/O interfaces work correctly (see section 4.2.2).

### 2.4 SIM interface

SIM card detection is not supported by "00" product version.

SARA-N3 series modules include a SIM interface on the VSIM, SIM\_IO, SIM\_CLK and SIM\_RST pins, which can operate at 1.8 V and/or 3.0 V voltage (VSIM domain). Activation and deactivation of the SIM interface, with automatic 1.8 V / 3.0 V voltage switch according to the voltage class of the external SIM connected to the module are implemented according to the ISO-IEC 7816-3 specifications.

SARA-N3 series modules include also the **GPIO5** pin to detect the presence of an external SIM card, as intended to be appropriately connected to the mechanical switch of an external SIM card holder. The **GPIO5** pin operates at the **V\_INT** voltage, which can be set to 1.8 V or 2.8 V using the **VSEL** input.

If a 3.0 V SIM is used, the VCC voltage shall be inside normal operating range to let the SIM interface work correctly (see section 4.2.2).

### 2.5 Serial interfaces

SARA-N3 series modules include the following serial interfaces:

- UART: main primary serial interface, for communication with host processor (2.5.1)

- UART AUX: auxiliary secondary serial interface for communication with host processor (2.5.2)

- UART FT: additional serial interface for Firmware update and Tracing (2.5.3)

- DDC: I2C-bus compatible interface for communication with I2C devices and sensors (2.5.4)

### 2.5.1 Main primary serial interface (UART)

SARA-N3 series modules include a main primary unbalanced asynchronous serial interface (UART) available for communication with an application host processor:

- AT communication

- FW upgrades by means of the FOAT feature

The characteristics of the main primary serial interface (UART) are:

- Complete serial port with RS-232 functionality conforming to ITU-T V.24 recommendation [4]

- CMOS compatible signal levels (0 V for low data bit or ON state and 1.8 V / 2.8 V for high data bit or OFF state): the internal power domain for the UART Interface is V\_INT, with voltage value set according to external VSEL pin configuration

- Data lines (**RXD** as output, **TXD** as input), hardware flow control lines (**CTS** as output, **RTS** as input), modem status and control lines (**DTR** as input, **DSR** as output, **DCD** as output, **RI** as output)

- Hardware flow control disabled by default

- UART works in low power idle mode, supporting 4800, 9600, 19200, 38400, 57600 b/s baud-rates

- One-shot automatic baud rate detection enabled by default

- 8N1 default frame format

The functionality of **DTR**, **DSR** and **DCD** lines is not supported by "00" product versions.

The UART interface settings can be suitably configured by AT commands (for more details, see the SARA-N2 / SARA-N3 series AT commands manual [1]).

#### 2.5.2 Secondary auxiliary serial interface (UART AUX)

The secondary auxiliary serial interface (UART AUX) is not supported by "00" product versions.

SARA-N3 series modules include a secondary auxiliary unbalanced asynchronous serial interface (UART AUX) available for communication with an application host processor

The characteristics of the secondary auxiliary serial interface (UART AUX) are:

- 2-wire serial port with RS-232 functionality conforming to ITU-T V.24 recommendation [4]

- CMOS compatible signal levels (0 V for low data bit or ON state and 1.8 V / 2.8 V for high data bit or OFF state): the internal power domain for the UART AUX Interface is **V\_INT**, with voltage value set according to external **VSEL** pin configuration

- Data lines (**RXD\_AUX** as output, **TXD\_AUX** as input)

The UART AUX interface settings can be suitably configured by AT commands (for more details, see the SARA-N2 / SARA-N3 series AT commands manual [1]).

#### 2.5.3 Additional serial interface for FW upgrade and Tracing (UART FT)

SARA-N3 series modules include an additional unbalanced asynchronous serial interface available for Firmware upgrade and Tracing (UART FT):

- FW upgrades by means of the u-blox EasyFlash tool

- Diagnostic purpose

The characteristics of the additional serial interface for Firmware upgrade and Tracing (UART FT) are:

- 2-wire serial port with RS-232 functionality conforming to ITU-T V.24 recommendation [4]

- CMOS compatible signal levels (0 V for low data bit or ON state and 1.8 V / 2.8 V for high data bit or OFF state): the internal power domain for the UART FT interface is V\_INT, with voltage value set according to external VSEL pin configuration

- Data lines (RXD\_FT as output, TXD\_FT as input)

For diagnostic and FW update purposes, connect test points to the **RXD\_FT** and **TXD\_FT** pins.

The trace diagnostic log is temporarily stopped when the module is in deep-sleep mode.

### 2.5.4 DDC (I2C) interface

The DDC (I2C) interface is not supported by "00" product versions.

SARA-N3 series modules include an I2C-bus compatible DDC interface (**SDA** data input/output, **SCL** clock output) available for the communication with external I2C devices and sensors.

The internal power domain for the I2C-bus compatible DDC interface is  $V_{INT}$ , with 1.8 V / 2.8 V voltage value set according to external VSEL pin configuration.

### 2.6 ADC

SARA-N3 series modules include two Analog-to-Digital Converter input pins, **ANT\_DET** and **ADC1**, configurable via a dedicated AT command (for further details, see the SARA-N2 / SARA-N3 series AT commands manual [1]).

### 2.7 GPIO

SARA-N3 series modules include General Purpose Input/Output pins that can be configured via u-blox AT commands (for further details, see the SARA-N2 / SARA-N3 series AT commands manual [1]).

The internal power domain for the GPIO pins is  $V_{INT}$ , with 1.8 V/2.8 V voltage value set according to external VSEL pin configuration.

Table 4 summarizes the custom functions available on the GPIO pins of SARA-N3 series modules.

| Function                  | Description                                                                                                             | Default GPIO                             | Configurable GPIOs                                    |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------|

| Network status indication | Output to indicate the network status:<br>registered home network, registered<br>roaming, data transmission, no service |                                          | GPIO1, GPIO2, CTS                                     |

| Module status indication  | Output indicating module status: power-off, sleep or deep-sleep mode versus idle, active or connected mode              |                                          | GPIO4                                                 |

| Last gasp                 | Input to trigger last gasp execution                                                                                    |                                          | GPIO3                                                 |

| SIM card detection        | Input to sense external SIM card physical presence                                                                      | GPIO5 <sup>4</sup>                       | GPIO5 <sup>4</sup>                                    |

| HW flow control (RTS)     | UART request to send input                                                                                              | RTS                                      | RTS                                                   |

| HW flow control (CTS)     | UART clear to send output                                                                                               | CTS                                      | CTS                                                   |

| Ring indication           | UART ring indicator output                                                                                              | RI                                       | RI                                                    |

| General purpose input     | Input to sense high or low digital level                                                                                |                                          | GPIO1, GPIO2,<br>GPIO3, GPIO4, GPIO5,<br>RI, RTS, CTS |

| General purpose output    | Output to set high or low digital level                                                                                 |                                          | GPIO1, GPIO2,<br>GPIO3, GPIO4, GPIO5,<br>RI, RTS, CTS |

| Pin disabled              | Output tri-stated, with an internal active pull-down enabled                                                            | GPIO1, GPIO2,<br>GPIO3, GPIO4,<br>GPIO5⁵ | GPIO1, GPIO2,<br>GPIO3, GPIO4,<br>GPIO5, RI, RTS, CTS |

Table 4: GPIO custom functions configuration

<sup>&</sup>lt;sup>4</sup> Not supported by "00" product version.

<sup>&</sup>lt;sup>5</sup> On "00" product version only.

## 3 Pin definition

### 3.1 Pin assignment

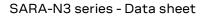

Figure 2: SARA-N3 series modules pin assignment

| No | Name    | Power<br>domain | I/O      | Description                             | Remarks                                                                                                                                                                                                                                                                                                                                    |

|----|---------|-----------------|----------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | GND     | GND             | N/A      | Ground                                  | All GND pads must be connected to ground.                                                                                                                                                                                                                                                                                                  |

| 2  | V_BCKP  | -               | I/O      | Real Time Clock<br>supply input/output  | See section 4.2.2 for detailed electrical specs.                                                                                                                                                                                                                                                                                           |

| 3  | GND     | GND             | N/A      | Ground                                  | All GND pads must be connected to ground.                                                                                                                                                                                                                                                                                                  |

| 4  | V_INT   | -               | Ο        | Digital I/O interfaces<br>supply output | V_INT supply output, rail of the Digital I/O interfaces,<br>generated by the module when switched-on.<br>V_INT = 1.8 V (typical), if VSEL pin is connected to GND.<br>V_INT = 2.8 V (typical), if VSEL pin is unconnected.<br>Test-point recommended for diagnostic purpose.<br>See section 4.2.2 for detailed electrical characteristics. |

| 5  | GND     | GND             | N/A      | Ground                                  | All GND pads must be connected to ground.                                                                                                                                                                                                                                                                                                  |

| 6  | DSR     | GDI             | 0        | UART data set ready                     | DSR not supported by '00' product versions.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical specs.                                                                                                                                                                                                                          |

| 7  | RI      | GDI             | 0        | UART ring indicator                     | Circuit 125 (RI) in ITU-T V.24.<br>PU/PD class b.<br>Configurable as GPIO, as described in section 2.7.<br>See section 4.2.8 for detailed electrical specs.                                                                                                                                                                                |

| 8  | DCD     | GDI             | 0        | UART data carrier<br>detect             | DCD not supported by '00' product versions.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical specs.                                                                                                                                                                                                                          |

| 9  | DTR     | GDI             | I        | UART data terminal<br>ready             | DTR not supported by '00' product versions.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical specs.                                                                                                                                                                                                                          |

| 10 | RTS     | GDI             | I        | UART request to send                    | Circuit 105 (RTS) in ITU-T V.24.<br>Internal active pull-up enabled, if HW flow control enabled<br>PU/PD class b.<br>Configurable as GPIO, as described in section 2.7.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                      |

| 11 | CTS     | GDI             | 0        | UART clear to send                      | Circuit 106 (CTS) in ITU-T V.24.<br>PU/PD class b.<br>Configurable as GPIO, as described in section 2.7.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                                                                                     |

| 12 | ТХD     | GDI             | I        | UART data input                         | Circuit 103 (TxD) in ITU-T V.24.<br>Internal active pull-up enabled.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                                                                                                       |

| 13 | RXD     | GDI             | 0        | UART data output                        | Circuit 104 (RxD) in ITU-T V.24.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                                                                                                                                           |

| 14 | GND     | GND             | N/A      | Ground                                  | All GND pads must be connected to ground.                                                                                                                                                                                                                                                                                                  |

| 15 | PWR_ON  | PWR_ON          | ,<br>N/A | Power-on input                          | Internal active pull-up enabled.<br>See section 4.2.5 for detailed electrical characteristics.<br>For diagnostic purposes, connect a test point to this pin                                                                                                                                                                                |

| 16 | GPIO1   | GDI             | I/O      | GPIO                                    | GPIO configurable as described in section 2.7.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                                                                                                                             |

| 17 | TXD_AUX | GDI             | I        | UART AUX data input                     | TXD_AUX not supported by '00' product versions.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                                                                                                                            |

| 18 | RESET_N | RESET_N         | I        | External reset input                    | Internal active pull-up enabled.<br>See section 4.2.6 for detailed electrical characteristics.<br>For diagnostic purposes, connect a test point to this pin.                                                                                                                                                                               |

| No | Name    | Power<br>domain | I/O | Description             | Remarks                                                                                                                                                                                                                              |

|----|---------|-----------------|-----|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19 | RXD_AUX | GDI             | 0   | UART AUX data<br>output | RXD_AUX not supported by '00' product versions.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                      |

| 20 | GND     | GND             | N/A | Ground                  | All GND pads must be connected to ground.                                                                                                                                                                                            |

| 21 | VSEL    | -               | I   | Voltage selection       | Input to select the operating voltage of the digital I/O<br>interfaces of the module (UART, I2C and GPIO pins).<br>V_INT = 1.8 V (typical), if VSEL pin is connected to GND.<br>V_INT = 2.8 V (typical), if VSEL pin is unconnected. |

| 22 | GND     | GND             | N/A | Ground                  | All GND pads must be connected to ground.                                                                                                                                                                                            |

| 23 | GPIO2   | GDI             | I/O | GPIO                    | GPIO configurable as described in section 2.7.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                       |

| 24 | GPIO3   | GDI             | I/O | GPIO                    | GPIO configurable as described in section 2.7.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                       |

| 25 | GPIO4   | GDI             | I/O | GPIO                    | GPIO configurable as described in section 2.7.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                       |

| 26 | SDA     | GDI             | I/O | I2C bus data line       | I2C interface not supported by '00' product versions.<br>Internal pull-up to V_INT.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                    |

| 27 | SCL     | GDI             | 0   | I2C bus clock line      | I2C interface not supported by '00' product versions.<br>Internal pull-up to V_INT.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                    |

| 28 | RXD_FT  | GDI             | 0   | UART FT data output     | For firmware update and trace log diagnostic purposes,<br>connect a test point to this pin.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                                                          |

| 29 | TXD_FT  | GDI             | I   | UART FT data input      | For firmware update and trace log diagnostic purposes,<br>connect a test point to this pin.<br>Internal active pull-up enabled.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                      |

| 30 | GND     | GND             | N/A | Ground                  | All GND pads must be connected to ground.                                                                                                                                                                                            |

| 31 | RSVD    | -               | N/A | RESERVED pin            | Leave unconnected.                                                                                                                                                                                                                   |

| 32 | GND     | GND             | N/A | Ground                  | All GND pads must be connected to ground.                                                                                                                                                                                            |

| 33 | ADC1    | ADC             | I   | ADC input               | 10-bit Analog to Digital Converter input.<br>This pin can be externally connected to GND, if the ADC<br>function is not needed in the application.<br>See section 4.2.9 for detailed electrical characteristics.                     |

| 34 | RSVD    | -               | N/A | RESERVED pin            | Leave unconnected.                                                                                                                                                                                                                   |

| 35 | RSVD    | -               | N/A | RESERVED pin            | Leave unconnected.                                                                                                                                                                                                                   |

| 36 | RSVD    | -               | N/A | RESERVED pin            | Leave unconnected.                                                                                                                                                                                                                   |

| 37 | RSVD    | -               | N/A | RESERVED pin            | Leave unconnected.                                                                                                                                                                                                                   |

| 38 | SIM_CLK | SIM             | 0   | SIM clock               | See section 4.2.7 for detailed electrical specs.                                                                                                                                                                                     |

| 39 | SIM_IO  | SIM             | I/O | SIM data                | See section 4.2.7 for detailed electrical specs.                                                                                                                                                                                     |

| 40 | SIM_RST | SIM             | 0   | SIM reset               | See section 4.2.7 for detailed electrical specs.                                                                                                                                                                                     |

| 41 | VSIM    | -               | 0   | SIM supply output       | See section 4.2.2 for detailed electrical characteristics.                                                                                                                                                                           |

| 42 | GPIO5   | GDI             | I/O | GPIO                    | GPIO configurable as described in section 2.7.<br>PU/PD class b.<br>See section 4.2.8 for detailed electrical characteristics.                                                                                                       |

| No    | Name    | Power<br>domain | I/O | Description         | Remarks                                                                                                           |

|-------|---------|-----------------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------|

| 43    | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

| 44    | RSVD    | -               | N/A | RESERVED pin        | Leave unconnected.                                                                                                |

| 45    | RSVD    | -               | N/A | RESERVED pin        | Leave unconnected.                                                                                                |

| 46    | RSVD    | -               | N/A | RESERVED pin        | Leave unconnected.                                                                                                |

| 47    | RSVD    | -               | N/A | RESERVED pin        | Leave unconnected.                                                                                                |

| 48    | RSVD    | -               | N/A | RESERVED pin        | Leave unconnected.                                                                                                |

| 49    | RSVD    | -               | N/A | RESERVED pin        | Leave unconnected.                                                                                                |

| 50    | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

| 51    | VCC     | VCC             | I   | Module supply input | All VCC pins must be connected to external supply.<br>See 4.2.2 and 4.2.3 for detailed electrical characteristics |

| 52    | VCC     | VCC             | I   | Module supply input | All VCC pins must be connected to external supply.<br>See 4.2.2 and 4.2.3 for detailed electrical characteristics |

| 53    | VCC     | VCC             | I   | Module supply input | All VCC pins must be connected to external supply.<br>See 4.2.2 and 4.2.3 for detailed electrical characteristics |

| 54    | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

| 55    | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

| 56    | ANT     | -               | I/O | RF cellular antenna | 50 $\Omega$ nominal characteristic impedance. See section 4.2.4 for detailed RF characteristics.                  |

| 57    | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

| 58    | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

| 59    | ANT_BT  | -               | I/O | RF BT antenna       | Bluetooth not supported by '00' product versions. 50 $\Omega$ nominal characteristic impedance.                   |

| 60    | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

| 61    | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

| 62    | ANT_DET | ADC             | I   | Antenna detection   | 10-bit Analog to Digital Converter input.<br>See section 4.2.8 for detailed electrical characteristics.           |

| 63    | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

| 64    | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

| 65-96 | GND     | GND             | N/A | Ground              | All GND pads must be connected to ground.                                                                         |

Table 5: SARA-N3 series modules pin-out

For an explanation of abbreviations and terms used, see appendix A.

## 4 Electrical specification

- Stressing the device above one or more of the ratings listed in the Absolute maximum rating section may cause permanent damage. These are stress ratings only. Operating the module at these or at any conditions other than those specified in the Operating conditions section (section 4.2) of the specification should be avoided. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- Electrical characteristics are defined according to the verification on a representative number of samples or according to the simulation.

- Where application information is given, it is advisory only and does not form part of the specification.

### 4.1 Absolute maximum rating

Limiting values given below are in accordance with Absolute Maximum Rating System (IEC 134).

| Symbol  | Description                | Condition                                           | Min. | Max. | Unit |

|---------|----------------------------|-----------------------------------------------------|------|------|------|

| VCC     | Module supply voltage      | Input DC voltage at VCC pin                         | -0.2 | 4.2  | V    |

| V_BCKP  | RTC supply voltage         | Input DC voltage at V_BCKP pin                      | -0.2 | 3.4  | V    |

| GDI     | Generic digital interfaces | Input DC voltage at Generic digital interfaces pins | -0.2 | 3.0  | V    |

| PWR_ON  | Power-on signal            | Input DC voltage at PWR_ON pin                      | -0.2 | 1.3  | V    |

| RESET_N | External reset signal      | Input DC voltage at RESET_N pin                     | -0.2 | 1.3  | V    |

| ADC     | ADC signal                 | Input DC voltage at ANT_DET and ADC pins            | -0.2 | 2.0  | V    |

Table 6: Absolute maximum ratings

The product is not protected against overvoltage or reversed voltages. If necessary, voltage spikes exceeding the power supply voltage specification given in table above must be limited to values within the specified boundaries by using appropriate protection devices.

### 4.1.1 Maximum ESD

| Parameter I                  |  | Typical | Max  | Unit | Remarks                                       |

|------------------------------|--|---------|------|------|-----------------------------------------------|

| ESD sensitivity for all pins |  |         | 1000 | V    | Human Body Model according to JS-001-2017     |

|                              |  |         | 500  | V    | Charged Device Model according to JS-002-2018 |

#### Table 7: Maximum ESD ratings

u-blox cellular modules are Electrostatic Sensitive Devices and require special precautions when handling. See section 7.4 for ESD handling instructions.

### 4.2 Operating conditions

- Unless otherwise indicated, all operating condition specifications are at an ambient temperature of +25 °C.

- △ Operation beyond the operating conditions is not recommended and extended exposure beyond them may affect device reliability.

### 4.2.1 Operating temperature range

| Parameter                      | Min | Typical | Max | Unit | Remarks                                                                                      |

|--------------------------------|-----|---------|-----|------|----------------------------------------------------------------------------------------------|

| Normal operating temperature   | -20 | +25     | +85 | °C   | Operating within 3GPP / ETSI specifications                                                  |

| Extended operating temperature | -40 |         | +85 | °C   | Operating with possible slight deviation in RF<br>performance outside normal operating range |

**Table 8: Environmental conditions**

### 4.2.2 Supply/power pins

| Pin name | Parameter                                                   | Min | Typical | Max | Unit |

|----------|-------------------------------------------------------------|-----|---------|-----|------|

| VCC      | Module supply normal operating input voltage <sup>6</sup>   | 3.2 | 3.8     | 4.2 | V    |

|          | Module supply extended operating input voltage <sup>7</sup> | 2.6 |         | 4.2 | V    |

| V_BCKP   | Real Time Clock supply input voltage                        | 1.6 |         | 3.3 | V    |

#### Table 9: Input characteristics of Supply/Power pins

| Pin name | Parameter                                                      | Min | Typical | Max | Unit |

|----------|----------------------------------------------------------------|-----|---------|-----|------|

| VSIM     | SIM interface supply output voltage, external SIM = 1.8V type  |     | 1.8     |     | V    |

|          | SIM interface supply output voltage, external SIM = 3.0V type  |     | 3.0     |     | V    |

| V_BCKP   | Real Time Clock supply output voltage                          |     | 2.5     |     | V    |

|          | Real Time Clock supply output current capability               |     |         | 0.5 | mA   |

| V_INT    | Digital I/O interfaces supply output voltage, VSEL = GND       |     | 1.8     |     | V    |

|          | Digital I/O interfaces supply output voltage, VSEL unconnected |     | 2.8     |     | V    |

|          | Digital I/O interfaces supply output current capability        |     |         | 70  | mA   |

Table 10: Output characteristics of Supply/Power pins

<sup>&</sup>lt;sup>6</sup> Operating within 3GPP / ETSI specifications.

<sup>&</sup>lt;sup>7</sup> Operating with possible slight deviation in RF performance outside normal operating range. The input voltage has to be above the extended operating range minimum limit to switch-on the module and to avoid possible switch-off of the module.

### 4.2.3 Current consumption

| Mode                                             | Condition                                                               | Tx power | Min | Тур <sup>8</sup> | Max | Unit |

|--------------------------------------------------|-------------------------------------------------------------------------|----------|-----|------------------|-----|------|

| Power-off mode                                   | Average current value<br>(power-off mode)                               |          |     | 3                |     | μA   |

| PSM deep-sleep mode                              | Average current value<br>(PSM deep-sleep mode)                          |          |     | 3                |     | μA   |

| Cyclic deep-sleep / active mode<br>(+NVSETPM: 9) | Average current value<br>(rock bottom)                                  |          |     | 3                |     | μA   |

|                                                  | Average current value<br>(DRX = 2.56 s, PTW = 20.48 s, eDRX = 655.36 s) |          |     | 50               |     | μΑ   |

| Cyclic sleep / active mode<br>(+NVSETPM: 9)      | Average current value<br>(rock bottom)                                  |          |     | 100              |     | μΑ   |

|                                                  | Average current value<br>(DRX = 2.56 s, PTW = 20.48 s, eDRX = 81.92 s)  |          |     | 230              |     | μΑ   |

|                                                  | Average current value<br>(DRX = 2.56 s, PTW = 5.12 s, eDRX = 20.48 s)   |          |     | 230              |     | μΑ   |

|                                                  | Average current value<br>(DRX = 2.56 s, no eDRX)                        |          |     | 0.6              |     | mA   |

|                                                  | Average current value<br>(DRX = 1.28 s, no eDRX)                        |          |     | 1.0              |     | mA   |

| Cyclic idle / active mode<br>(+NVSETPM : 1)      | Average current value<br>(rock bottom)                                  |          |     | 0.8              |     | mA   |

|                                                  | Average current value<br>(DRX = 2.56 s, no eDRX)                        |          |     | 1.2              |     | mA   |

|                                                  | Average current value<br>(DRX = 1.28 s, no eDRX)                        |          |     | 1.5              |     | mA   |

| Active mode<br>(+NVSETPM: 0)                     | Average current value<br>(DRX 1.28 s)                                   |          |     | 20               |     | mA   |

|                                                  | Average current value<br>(airplane mode, +CFUN: 0)                      |          |     | 11               |     | mA   |

| Connected mode                                   | Average current value<br>(Rx mode)                                      |          |     | 23               |     | mA   |

|                                                  | Average current value                                                   | –40 dBm  |     | 45               |     | mA   |

|                                                  | (Tx mode)                                                               | –10 dBm  |     | 55               |     | mA   |

|                                                  |                                                                         | 0 dBm    |     | 75               |     | mA   |

|                                                  |                                                                         | 8 dBm    |     | 120              |     | mA   |

|                                                  |                                                                         | 14 dBm   |     | 155              |     | mA   |

|                                                  |                                                                         | 20 dBm   |     | 235              |     | mA   |

|                                                  |                                                                         | Maximum  |     | 275              |     | mA   |

Table 11: VCC current consumption <sup>9</sup>

<sup>&</sup>lt;sup>8</sup> Typical values with a matched antenna.

<sup>&</sup>lt;sup>9</sup> Module current consumption through **VCC** input pins, in the listed modes/conditions.

### 4.2.4 RF characteristics

| Parameter                 |          | Min  | Max  | Unit | Remarks         |

|---------------------------|----------|------|------|------|-----------------|

| Frequency range<br>Band 3 | Uplink   | 1710 | 1785 | MHz  | Module transmit |

|                           | Downlink | 1805 | 1880 | MHz  | Module receive  |

| Frequency range           | Uplink   | 824  | 849  | MHz  | Module transmit |

| Band 5                    | Downlink | 869  | 894  | MHz  | Module receive  |

| Frequency range           | Uplink   | 880  | 915  | MHz  | Module transmit |

| Band 8                    | Downlink | 925  | 960  | MHz  | Module receive  |

| Frequency range           | Uplink   | 832  | 862  | MHz  | Module transmit |

| Band 20                   | Downlink | 791  | 821  | MHz  | Module receive  |

| Frequency range           | Uplink   | 703  | 748  | MHz  | Module transmit |

| Band 28                   | Downlink | 758  | 803  | MHz  | Module receive  |

Table 12: Operating RF frequency bands

| Parameter                  | Min. | Typical | Max. | Unit | Remarks                      |

|----------------------------|------|---------|------|------|------------------------------|

| Receiver input sensitivity |      | -140    |      | dBm  | Maximum possible repetitions |

Table 13: Receiver sensitivity performance

### 4.2.5 PWR\_ON pin

| Parameter                                  | Min. | Typical | Max. | Unit | Remarks                                     |

|--------------------------------------------|------|---------|------|------|---------------------------------------------|

| Internal supply for<br>PWR_ON Input Signal |      | 1.1     |      | V    | Internal supply rail                        |

| Low-level input                            | 0.0  |         | 0.2  | V    |                                             |

| High-level input                           | 0.9  |         | 1.1  | V    |                                             |

| Pull-up resistance                         |      | 90      |      | kΩ   | Internal active pull-up                     |

| PWR_ON low-level time                      | 1    |         | 2.5  | S    | Low time to trigger module switch-on        |

|                                            | 1    |         | 2.5  | S    | Low time to trigger module wake-up from PSM |

|                                            | 2.5  |         |      | s    | Low time to trigger module switch-off       |

Table 14: PWR\_ON pin characteristics

### 4.2.6 RESET\_N pin

| Parameter                                   | Min. | Typical | Max. | Unit | Remarks                                    |

|---------------------------------------------|------|---------|------|------|--------------------------------------------|

| Internal supply for<br>RESET_N Input Signal |      | 1.1     |      | V    | Internal supply rail                       |

| Low-level input                             | 0.0  |         | 0.2  | V    |                                            |

| High-level input                            | 0.9  |         | 1.1  | V    |                                            |

| Pull-up resistance                          |      | 70      |      | kΩ   | Internal active pull-up                    |

| RESET_N low-level time                      | 1    |         |      | S    | Low time to trigger module reset (re-boot) |

Table 15: RESET\_N pin characteristics

### 4.2.7 SIM interface pins

| Parameter                  | Min.     | Typical | Max.     | Unit | Remarks                            |

|----------------------------|----------|---------|----------|------|------------------------------------|

| Internal supply domain for |          | 1.8     |          | V    | VSIM, with external 1.8 V SIM type |

| SIM interface              |          | 3.0     |          | V    | VSIM, with external 3.0 V SIM type |

| Low-level input            | 0.0      |         | 0.3*VSIM | V    |                                    |

| High-level input           | 0.7*VSIM |         | VSIM     | V    |                                    |

| Low-level output           |          | 0.0     |          | V    |                                    |

| High-level output          |          | VSIM    |          | V    |                                    |

| Internal pull-up on SIM_IO |          | 4.7     |          | kΩ   | Internal pull-up to VSIM           |

| Clock frequency on SIM_CLK |          | 3       |          | MHz  |                                    |

|                            |          |         |          |      |                                    |

Table 16: SIM pins characteristics

### 4.2.8 Generic Digital Interface pins

| Min.      | Typical | Max.                                                 | Unit                                                                                                 | Remarks                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------|------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1.8     |                                                      | V                                                                                                    | V_INT, with VSEL connected to GNE                                                                                                                                                                                                                                                                                                                             |